一、不同容量EEPROM区别

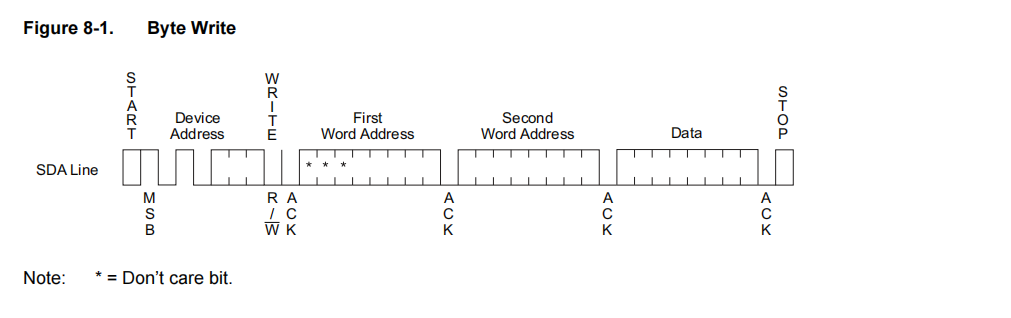

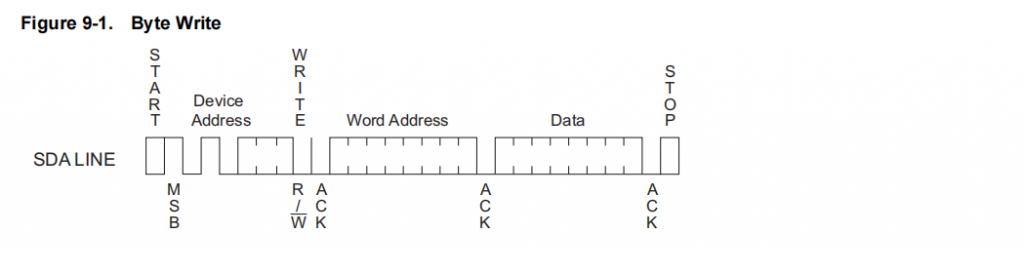

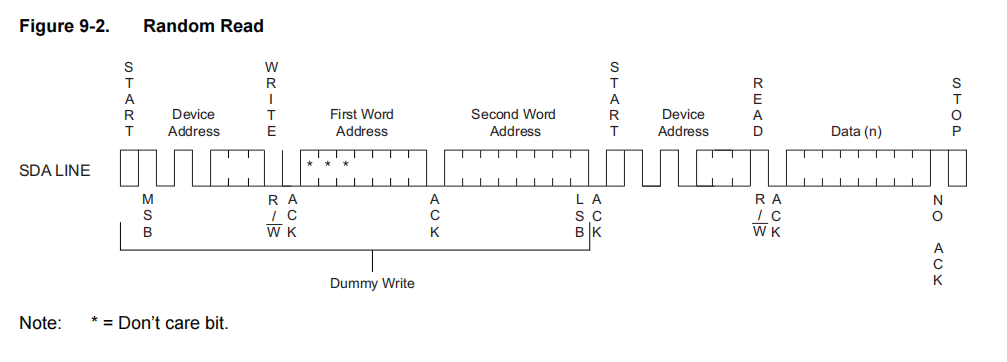

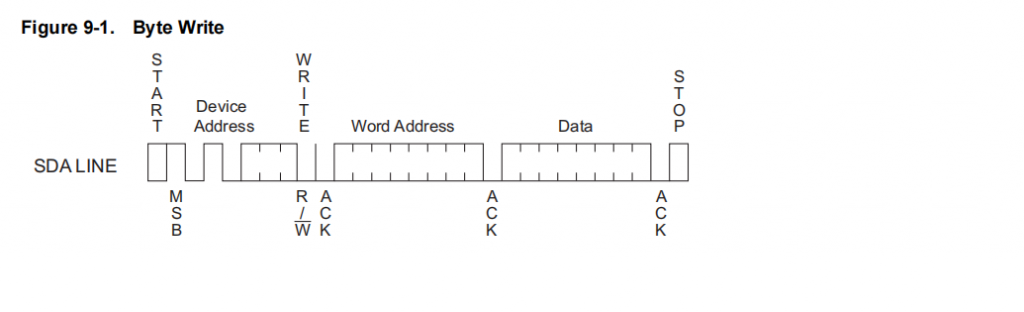

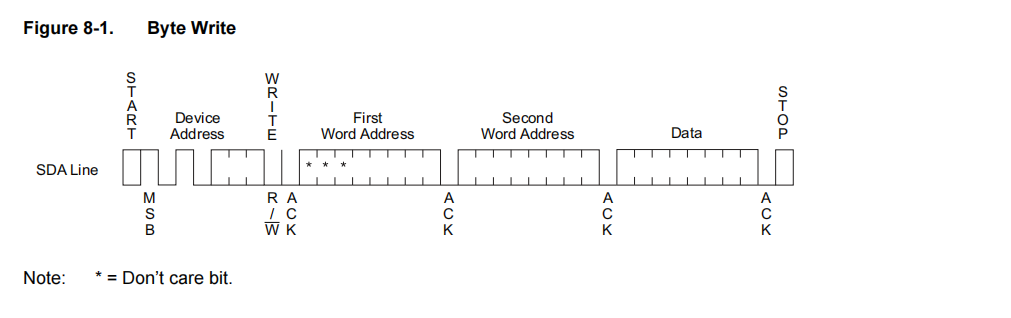

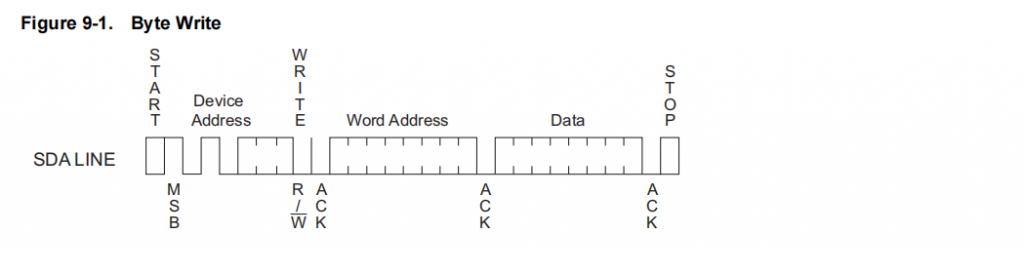

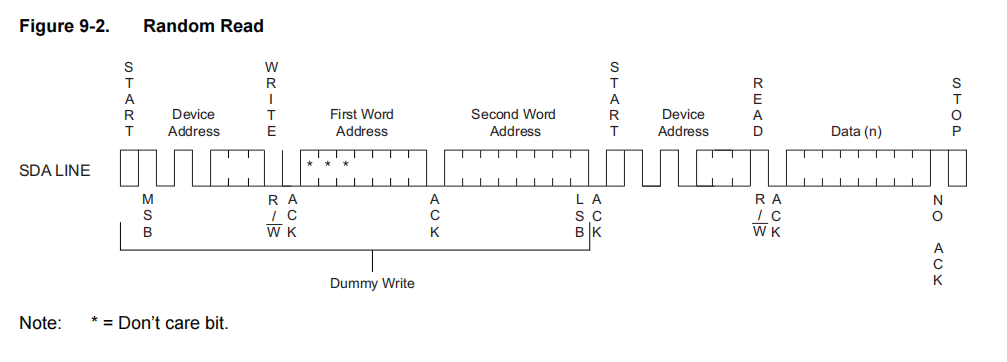

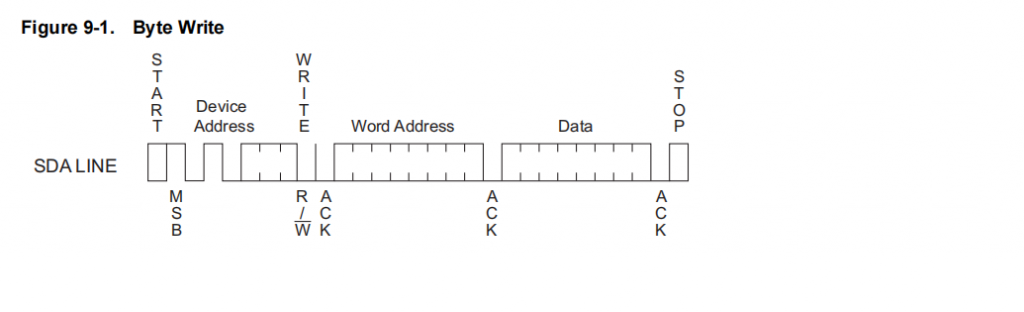

1、AT24C64和AT24C02容量不容页长度不一样

AT24C64D单页大小:64-Kbit (8,192 x 8)

AT24C02C单页大小:2-Kbit (256 x 8)

2、读写时序不同

注意:由于AT24C64D比AT24C02C页数量多,并且超过一个字节长度,所以AT24C64D页地址增加一个字节。

一、不同容量EEPROM区别

1、AT24C64和AT24C02容量不容页长度不一样

AT24C64D单页大小:64-Kbit (8,192 x 8)

AT24C02C单页大小:2-Kbit (256 x 8)

2、读写时序不同

注意:由于AT24C64D比AT24C02C页数量多,并且超过一个字节长度,所以AT24C64D页地址增加一个字节。

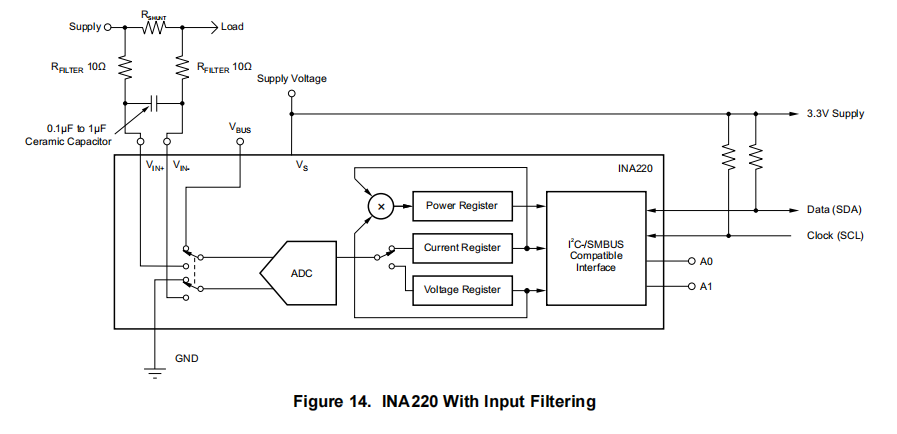

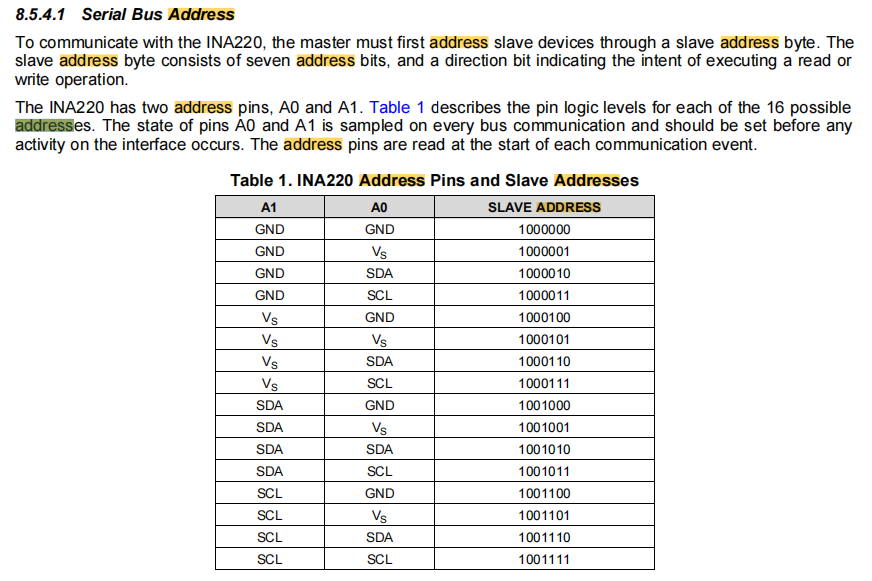

1、通讯支持I2c和SMBus接口协议,从机地址如下图所示:

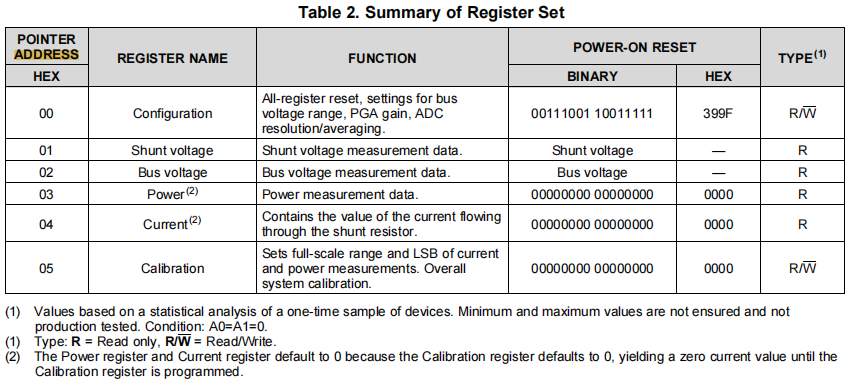

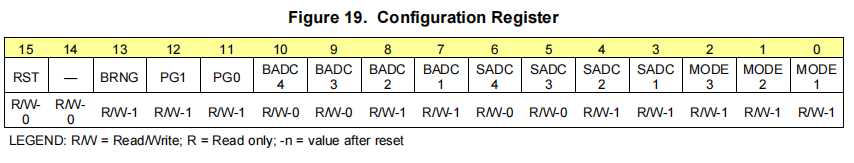

1、配置寄存器

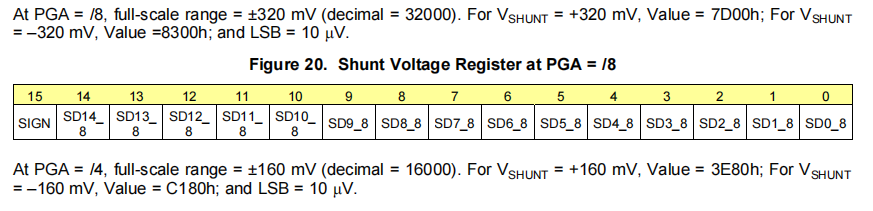

2、并联电压寄存器(根据配置寄存器参数有相应调整)

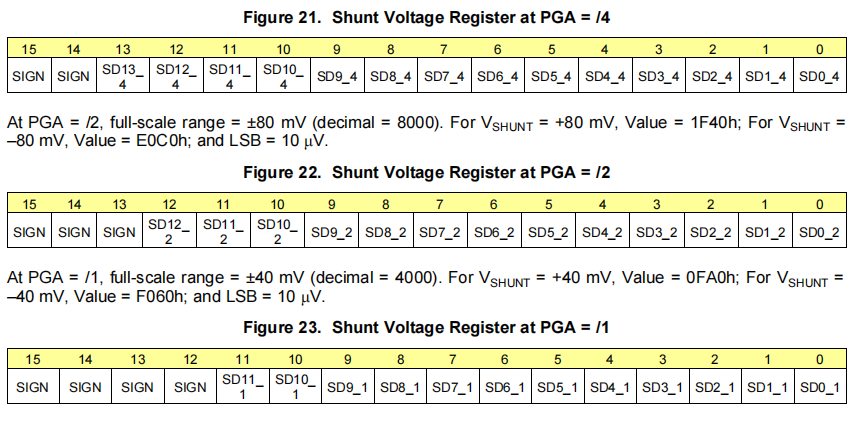

3、总电压寄存器

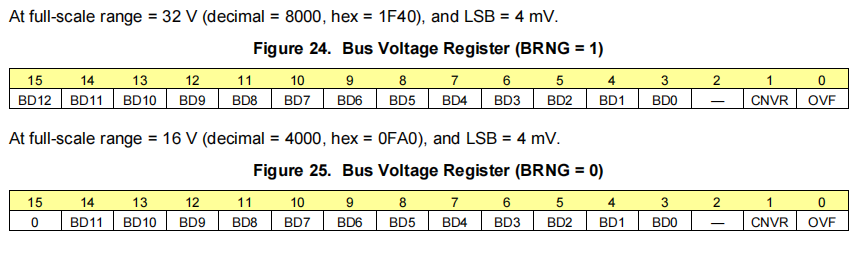

4、功率寄存器

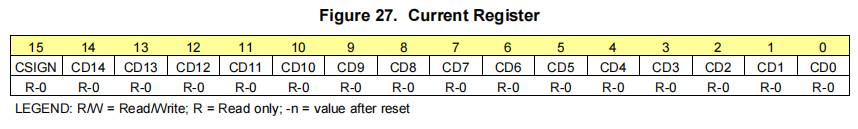

5、电流寄存器

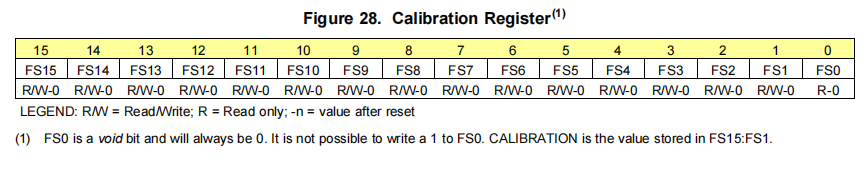

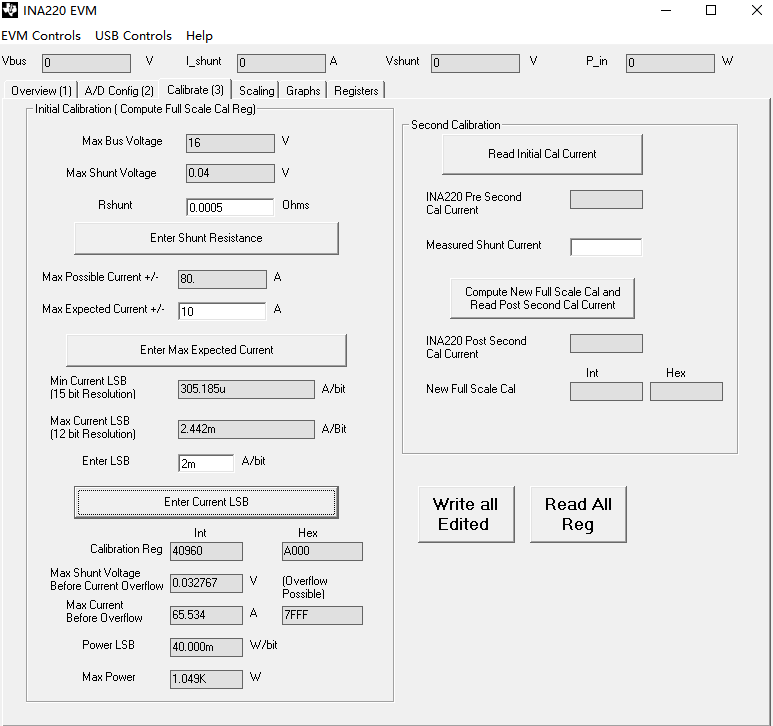

6、校准寄存器

1、并联电压

ShuntVoltage/ShuntVoltage(寄存器值)=320mV/7D00H

ShuntVoltage=ShuntVoltage(寄存器值)*320mV/7D00H

ShuntVoltage(mV)=ShuntVoltage(寄存器值)/100

2、总电压

BusVoltage=(BusVoltage(寄存器值)>>3)*32V/8000

3、电流

Current=ShuntVoltage(寄存器值)*校准寄存器值*LSB(mA)/(4096*1000)

4、功率值

Power=电流寄存器*电压寄存器*0.04(W)/5000

由于NXP为LX2160增加了硬件加密引擎与openssl接口,我们可以直接编译使用openssl API接口。

1、编译:

$ cd flexbuild

$ source setup.env

Build cryptodev-linux:

$ flex-builder -c cryptodev_linux -a arm64 # automatically setup cross-toolchain and fetch

cryptodev-linux repository to build

Build OpenSSL:

$ flex-builder -c openssl -a arm64

Merge OpenSSL and cryptodev-linux components into target rootfs:

$ flex-builder -i merge-component -a arm64

Generate bootpartition tarball:

$ flex-builder -i mkbootpartition -a arm64

flex-builder -i mkbootpartition -a arm64 -m lx2160ardb_rev2 -b sd2、配置:

cat /etc/ld.so.conf

include /etc/ld.so.conf.d/*.conf

修改为:

#include /etc/ld.so.conf.d/*.conf

# libc default configuration

/usr/local/lib

# Multiarch support

/usr/local/lib/aarch64-linux-gnu

/lib/aarch64-linux-gnu

/usr/lib/aarch64-linux-gnu

/usr/lib/aarch64-linux-gnu/libfakeroot3、加载模块

user@localhost:~$ sudo modprobe cryptodev

[sudo] password for user:

user@localhost:~$ ls /dev/crypto

/dev/crypto

user@localhost:~$ openssl engine

(devcrypto) /dev/crypto engine

(dynamic) Dynamic engine loading support4、Verify the CAAM offloading

Hardware operations can be monitored with the interrupt counters for CAAM JR and QI (DPAA1 and DPAA2) interfaces.

user@localhost:~$ cat /proc/interrupts | grep jr

78: 20 0 0 0 GICv2 103 Level 1710000.jr

79: 0 0 0 0 GICv2 104 Level 1720000.jr

80: 0 0 0 0 GICv2 105 Level fsl-jr0

user@localhost:~$ openssl enc -aes-256-cfb -k secret -P -md sha1

*** WARNING : deprecated key derivation used.

Using -iter or -pbkdf2 would be better.

salt=233157F098D1B0E8

key=D2B0C0C088AA7DAA6CF37CC856E283E3B0C3DD2BE155688DE18593EB3F997776

iv =A4E2C86E0DBA1211B5A4B02EBEFF6DC4

user@localhost:~$ cat /proc/interrupts | grep jr

78: 54 0 0 0 GICv2 103 Level 1710000.jr

79: 69 0 0 0 GICv2 104 Level 1720000.jr

80: 0 0 0 0 GICv2 105 Level fsl-jr05、DPDK加解密接口测试

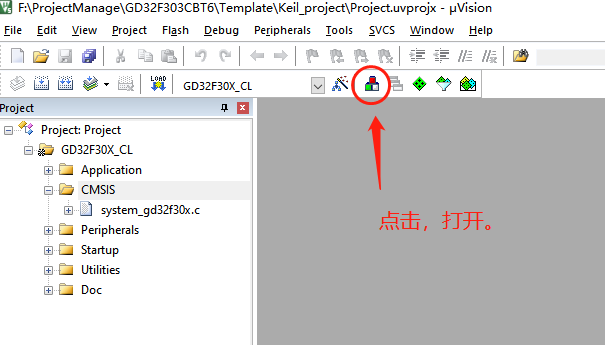

解决方式:将Project文件夹中的工程扩展名由.uvproj改为.uvprojx

问题原因:前提是所有的库安装都是正常且正确的,所以应该是如下问题:keil版本问题导致的Device导入错误,可能是使用keil4版本编写,使用keil5打开出错。

报错内容:

one or more devices family pack devices are not present

error:not found device

解决方式:安装库

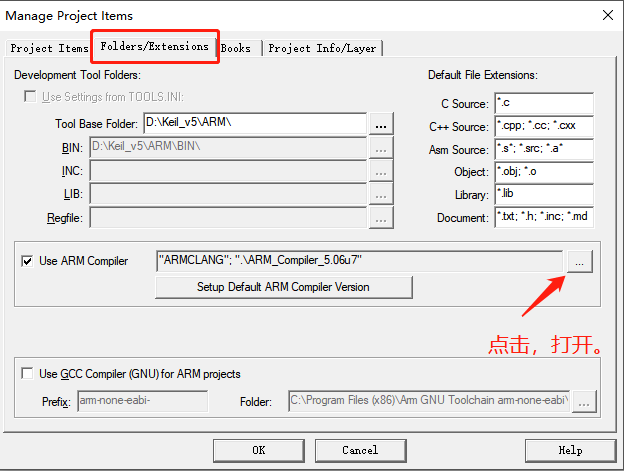

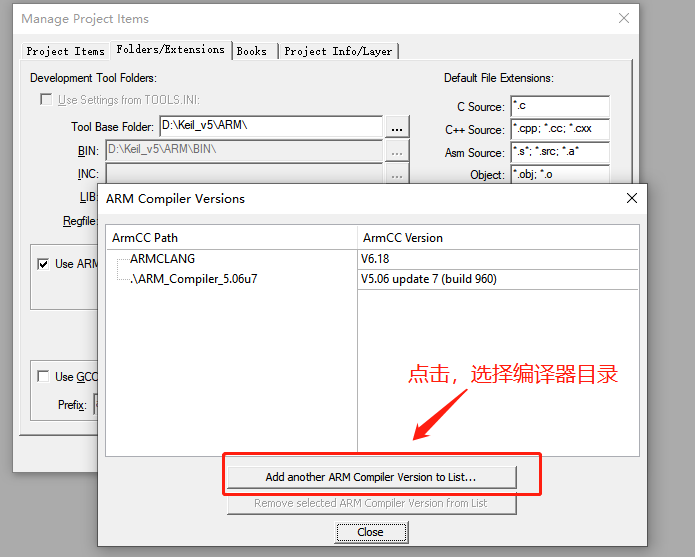

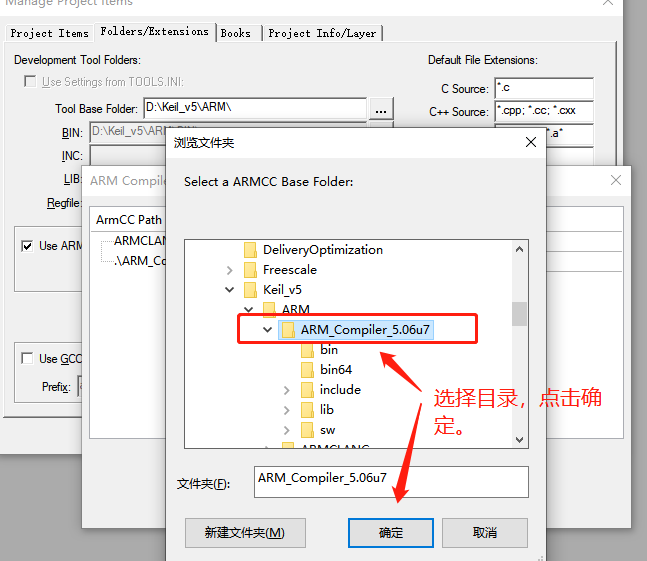

一、分析

通过字面意思可以得知目标程序需要arm版本5编译器.

二、解决

1、官网下载编译

2、安装

注意:要安装到D:\Keil_v5\ARM\ARM_Compiler_5.06u7。盘符可根据实际情况。

3、keil添加多编译器

在使用 repo sync 同步 Android 源码时,可以添加一些选项来减少同步时间和要下载的代码空间。具体的命令是 repo sync -c --no-tags --prune -j 4。

查看 repo help status 的帮助信息,对所给的各个选项具体说明如下:

git branch -r 命令看不到服务器新增的分支名。如果不加 -c 选项,那么同步的时候,会打印 [new branch] 这样的信息,使用 git branch -r 命令可查看到服务器新增的分支。--prune 选项,可以让本地仓库删除对这个分支的跟踪引用。查看 repo 的 .repo/repo/project.py 源码,这个选项实际上是作为 git fetch 命令的选项来执行。查看 man git-fetch 对自身 --prune 选项的说明如下,可供参考:-p, –prune-j 4 指定用4个线程来同步。如果没有提供该选项,默认是用2个线程。总的来说,在 repo sync -c --no-tags --prune -j 4 命令中,使用 -c 和 –no-tags 选项可以减少需要同步的内容,从而减少要占用的本地代码空间,也可以减少一些同步时间。

使用 -j 选项来指定启用多线程进行同步,可以加快执行速度,也就减少了同步时间。

使用 –prune 选项去掉已删除分支的跟踪引用,一般不会用到,这个选项可加可不加。

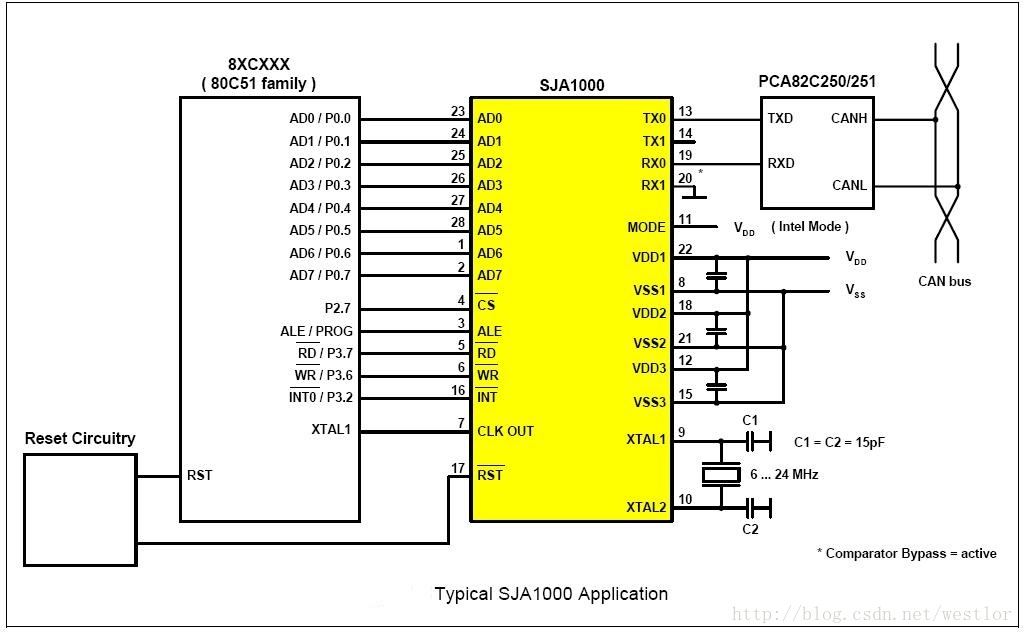

有时会需要扩展多个CAN接口,在CAN设备比较多的时候作分组控制。这里使用imx6q芯片,它本身已经自带了两个CAN接口,如果需再扩展4个接口,就要想想办法了。sja1000是一个经典的CAN控制器,稳定可靠,由于它在业界使用方案比较成熟,用它来扩展再好不过。imx6q作为一款性能强大的处理器,扩展sja1000这种相对慢速的芯片,着实有点屈才。可是没办法,项目需要,就像PCIE转ISA,或者USB转PCIE一样,效率并不是最重要的,硬件的兼容性和软件的易维护性同样重要。

这篇文档分硬件部分和软件部分来介绍下imx6q如何来与sja1000芯片组合应用起来,主要实现了通过imx6芯片的eim总线外扩4个sja1000 can控制器的功能。

首先来一张sja1000芯片的经典电路,是与8051单片机配合使用的。

看到这张图,是不是首先就想到了8051单片机的P0脚,还记得当时刚刚接触51单片机时,还会对P0与P1/P2/P3引脚的特性不同有些困惑。P0脚是3态的,可以应用在地址/数据总线。51单片机就是通过P0接口来扩展些SRAM、ROM啥的。这个电路图中,就是一个典型的外扩SRAM的接法:P0做地址/数据总线,P2.7独立GPIO控制CS脚(CS脚为低SJA1000芯片才工作),ALE/RO/WE是读写控制信号,INT中断脚接到P3.2接口上。从而可以看出,sja1000芯片留给外部的接口就是一个SRAM接口(CPU通过总线读写sja1000芯片的寄存器来控制),只要CPU有能够扩展SRAM的总线接口,那么就能外扩sja1000芯片。那么imx6芯片有没有类似的总线呢?

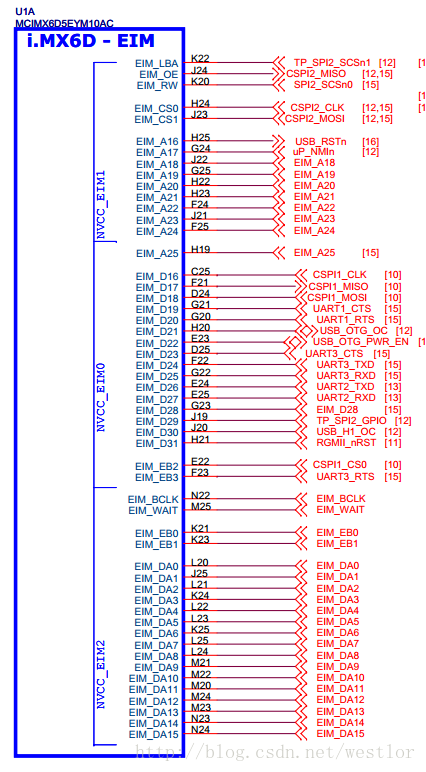

答案是肯定的,imx6系列芯片功能丰富,性能爆表,区区一个SRAM总线接口,怎会没有。imx6芯片带有WEIM接口,支持16/32bit的地址/数据总线混合模式,不过地址线最高为27bit,这个接口可灵活配置地址/数据端口,支持外接SRAM、NorFalsh和OneNAND等设备,先来看一张典型的imx6芯片的EIM接口图。

EIM总线地址总线引脚范围为EIM_DA0_15、EIM_A16_26,数据总线引脚范围为EIM_DA0_15、EIM_D16_31(图中有些引脚没有引出)。sja1000与之相连,可以是地址/数据总线复用的方式,也可以是地址总线与数据总线分离的方式(通过配置地址和数据引脚端口)。从电路简洁性上讲,当然采用复用的方式,就像51单片机的P0接口一样。有些芯片的SRAM接口并不支持地址/数据总线复用,与sja1000芯片相接时需要在电路上加逻辑器件,这个在另一篇文档中再写吧。

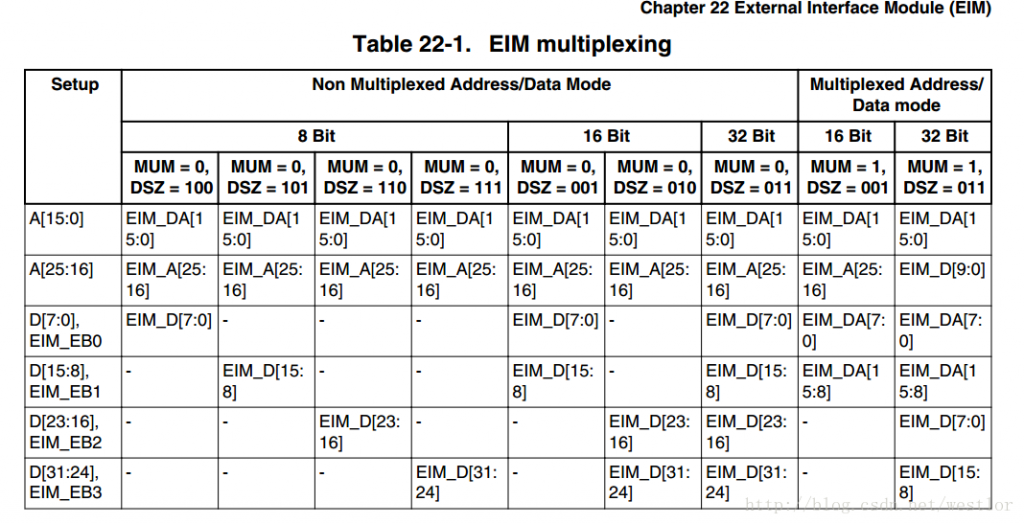

imx6芯片手册中指出,EIM总线只支持16/32bit的复用方式,通过EIM_CSnGCR1寄存器来配置,如下图。

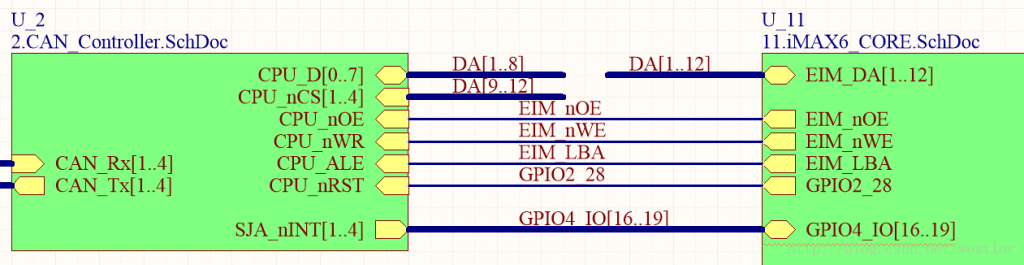

EIM总线与sja1000这种8位的SRAM接口类型芯片相连,用16bit的multiplexing模式搓搓有余。可以16位的总线来访问8位总线存储器时,会有地址无法对齐的尴尬情况。举个例子说,16位总线读地址0x0000时(忽略基地址),read_byte()读的是D0_7这一组的电平值,读地址0x0001时,read_byte(),读的是D8_15这一组的电平值,反之写操作也是一样。那么16位总线与sja1000相连时,如果只用DA0_7脚,必然导致虽偶地址访问正常,奇地址访问不到的情况。这个也好解决,我们用DA1_8引脚就可以了。整个连接起来如下图的样子。

其中EIM_nOE、EIM_nWE和EIM_LBA与51单片机的WR、RD和ALE类似,DA1_8为地址/数据复用总线的0_7位,DA9_12则用来当4个CS信号线用(接了4片SJA1000芯片),EIM总线有CS0_3,不过被其它功能引脚复用占了,这里就只能这么干了。至于RST和INT线,随便找几个GPIO就行。

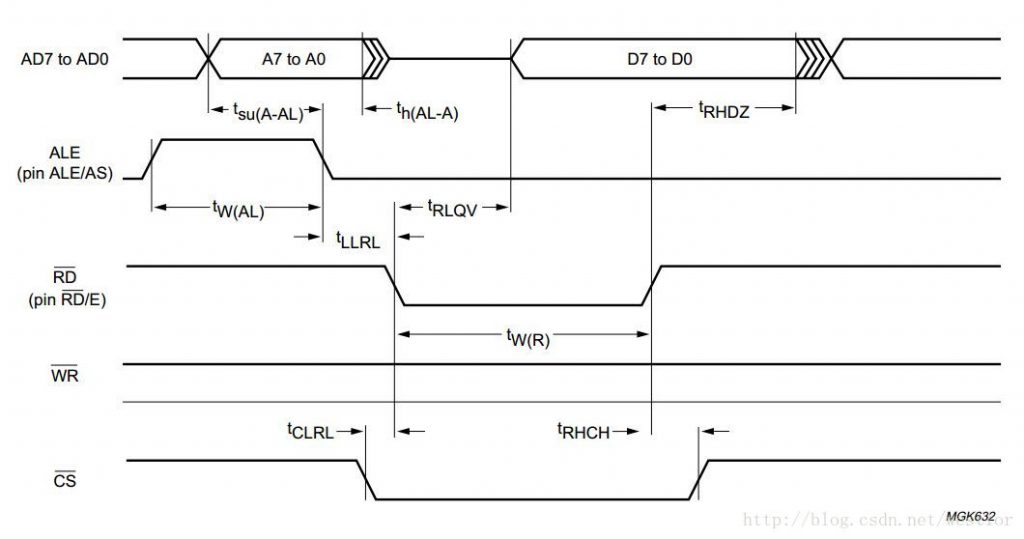

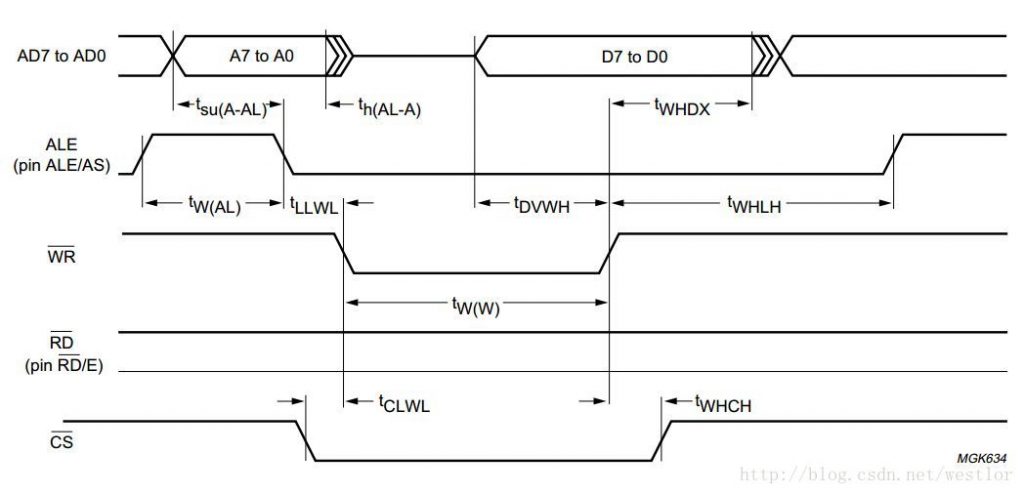

接下来简单分析下硬件时序,先看sja1000芯片的读时序。

从图中可以看出,读操作周期中,主机端先给出要读的地址(AD0_7上产生),然后拉低ALE信号,提示sja1000设备进行地址锁存,拉低CS信号,使能sja1000设备,最后拉低RD信号,释放地址/数据总线。sja1000设备在t_RLQV时间内准备好数据,然后写在数据总线上。主机在t_W/R时间后,拉高RD信号,读取地址/总线上的数据,拉高CS线,完成一个读操作周期。整个读操作周期中WR信号为高。写操作周期与之类似,如下图所示。

同样,主机端准备好地址信号,拉低ALE信号、CS信号,然后拉低WR信号,提示sja1000设备将进行写操作。之后主机端在地址/总线上写数据信号,等待t_DVWH后,拉高WR信号线,在t_WHDX时间后释放总线。sja100设备在拉高WR信号的时候进行接收数据。

这里使用的是3.14.28版本linux内核,由于支持设备树,为驱动程序的编写带来了很多便利。首先修改dts文件,使能WEIM总线,并配置需要用到的功能引脚、GPIO、中断引脚。

&weim {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_weim>;

status = "okay";

};

&iomuxc {

pinctrl_weim: weim1grp {

fsl,pins = <

MX6QDL_PAD_EIM_OE__EIM_OE_B 0x9091

MX6QDL_PAD_EIM_RW__EIM_RW 0x9091

MX6QDL_PAD_EIM_CS0__EIM_CS0_B 0x9091

MX6QDL_PAD_EIM_LBA__EIM_LBA_B 0x9091

/* SJA1000_RST */

MX6QDL_PAD_EIM_EB0__GPIO2_IO28 0x9091

/* SJA1000 INT */

MX6QDL_PAD_DI0_DISP_CLK__GPIO4_IO16 0x9091

MX6QDL_PAD_DI0_PIN15__GPIO4_IO17 0x9091

MX6QDL_PAD_DI0_PIN2__GPIO4_IO18 0x9091

MX6QDL_PAD_DI0_PIN3__GPIO4_IO19 0x9091

/* SJA1000 LED */

MX6QDL_PAD_DISP0_DAT5__GPIO4_IO26 0x80000000

MX6QDL_PAD_DISP0_DAT6__GPIO4_IO27 0x80000000

MX6QDL_PAD_DISP0_DAT7__GPIO4_IO28 0x80000000

MX6QDL_PAD_DISP0_DAT8__GPIO4_IO29 0x80000000

/* SJA1000_ADDA */

MX6QDL_PAD_EIM_DA0__EIM_AD00 0x9091

MX6QDL_PAD_EIM_DA1__EIM_AD01 0x9091

MX6QDL_PAD_EIM_DA2__EIM_AD02 0x9091

MX6QDL_PAD_EIM_DA3__EIM_AD03 0x9091

MX6QDL_PAD_EIM_DA4__EIM_AD04 0x9091

MX6QDL_PAD_EIM_DA5__EIM_AD05 0x9091

MX6QDL_PAD_EIM_DA6__EIM_AD06 0x9091

MX6QDL_PAD_EIM_DA7__EIM_AD07 0x9091

MX6QDL_PAD_EIM_DA8__EIM_AD08 0x9091

MX6QDL_PAD_EIM_DA9__EIM_AD09 0x9091

MX6QDL_PAD_EIM_DA10__EIM_AD10 0x9091

MX6QDL_PAD_EIM_DA11__EIM_AD11 0x9091

MX6QDL_PAD_EIM_DA12__EIM_AD12 0x9091

MX6QDL_PAD_EIM_DA13__EIM_AD13 0x9091

MX6QDL_PAD_EIM_DA14__EIM_AD14 0x9091

MX6QDL_PAD_EIM_DA15__EIM_AD15 0x9091

>;

};

};

};weim总线中配置的引脚有 EIM_DA0_15(只用到DA1_12)、EIM_OE、EIM_RW、EIM_LBA、EIM_CS0(cs线由高位地址线取代,这里无用),sja1000驱动中添加了四个中断引脚(对应4个sja1000芯片)、4个LED gpio(CAN通信指示灯用)、RST GPIO(产生硬复位信号,一般不用)。接下来看sja1000驱动需要添加的dts文件内容。

/ {

sja1000@08001C00 {

compatible = "weim,sja1000";

reg = <0x08001C00 0x1FF>;

nxp,external-clock-frequency = <16000000>;

nxp,tx-output-config = <0x16>;

nxp,no-comparator-bypass;

interrupt-parent = <&gpio4>;

interrupts = <16 0>;

int-gpios = <&gpio4 16 0>;

rst-gpios = <&gpio2 28 0>;

led-gpios = <&gpio4 26 0>;

};

sja1000@08001A00 {

compatible = "weim,sja1000";

reg = <0x08001A00 0x1FF>;

nxp,external-clock-frequency = <16000000>;

nxp,tx-output-config = <0x16>;

nxp,no-comparator-bypass;

interrupt-parent = <&gpio4>;

interrupts = <17 0>;

int-gpios = <&gpio4 17 0>;

led-gpios = <&gpio4 27 0>;

};

sja1000@08001600 {

compatible = "weim,sja1000";

reg = <0x08001600 0x1FF>;

nxp,external-clock-frequency = <16000000>;

nxp,tx-output-config = <0x16>;

nxp,no-comparator-bypass;

interrupt-parent = <&gpio4>;

interrupts = <18 0>;

int-gpios = <&gpio4 18 0>;

led-gpios = <&gpio4 28 0>;

};

sja1000@08000E00 {

compatible = "weim,sja1000";

reg = <0x08000E00 0x1FF>;

nxp,external-clock-frequency = <16000000>;

nxp,tx-output-config = <0x16>;

nxp,no-comparator-bypass;

interrupt-parent = <&gpio4>;

interrupts = <19 0>;

int-gpios = <&gpio4 19 0>;

led-gpios = <&gpio4 29 0>;

};

};四片sja1000芯片的基地址计算方式:weim总线的基地址为0x08000000,第一片sja1000芯片读写时DA1_8 对应地址/数据总线的D0_7,地址范围为 0x08000000~0x080001FF(忽略DA0的信号),由于DA9_12充当CS信号,读写第一片sja1000芯片时,需要保持DA9为0、DA10为1、DA11为1、DA12为1,从而第一片sja1000芯片的基地址为0x08001C00。同理,第二三四片sja1000芯片的基地址分别为 0x08001A00 、0x08001600、0x08000E00。

dts资源配置好后,需要在对应的驱动程序中正确引用。linux内核中已经有了sja1000_platform驱动(位于driver/net/can/sja1000目录下),直接在它的基础上修改下就行。

static struct of_device_id sp_of_table[] = {

{.compatible = "weim,sja1000"},

{},

};

MODULE_DEVICE_TABLE(of, sp_of_table);

static struct platform_driver sp_driver = {

.probe = sp_probe,

.remove = sp_remove,

.driver = {

.name = DRV_NAME,

.owner = THIS_MODULE,

.of_match_table = sp_of_table,

},

};2. 初始化weim总线

这里通过修改寄存器完成,程序在加载驱动程序时调用,主要配置weim时钟、中断、地址/数据总线端口、时序控制等,详见imx6数据手册。

static int __init sp_init(void)

{

mx6q_setup_weimcs();

return platform_driver_register(&sp_driver);

}

module_init(sp_init);

void mx6q_setup_weimcs(void)

{

unsigned int reg;

void __iomem *eim_reg = ioremap(WEIM_BASE_ADDR, 0x20);

void __iomem *ccm_reg = ioremap(CCM_BASE_ADDR, 0x80);

if(!eim_reg){

printk("error iomem eim_reg\n");

}

if(!ccm_reg){

printk("error iomem ccm_reg\n");

}

// divicer for aclk_eim_slow

reg = readl(ccm_reg + 0x1C);

reg &= ~(0x60000000);

reg |= 0x00380000;

writel(reg, ccm_reg + 0x1C);

/* CLKCTL_CCGR6: Set emi_slow_clock to be on in all modes */

reg = readl(ccm_reg + 0x80);

reg |= 0x00000C00;

writel(reg, ccm_reg + 0x80);

/* CS0GCR1:

* [22-20 CSREC: minimum EIM clock cycles width of CS, OE and WE signals]

* DSZ[16:18]:

001 16 bit port resides on DATA[15:0]

* EIM Operation Mode: MUM=1, SRD = SWR = 0.

* (Async write/Async page read, multiplexed)

*/

writel(0x07f13039, eim_reg);

writel(0x00001002, eim_reg + 0x00000004);

/* CS0RCR1:

* Bit 31 30 29 28--27 26 25 24--23 22 21 20--19 18 17 16

* 0 RWSC 0 RADVA RAL RADVN

* Bit 15 14 13 12--11 10 9--8 7 6 5 4--3 2 1 0

* 0 OEA 0 OEN 0 RCSA 0 RCSN

* CS0RCR2:

* APR = 0 (Async Page Read); [15]

* PAT = 7 (9 EIM clock sycles) [12:14]

* RBEA = 7 (Read BE Assertion) [4:6]

* RBE = 1 (Read BE enable) [3]

* RBEN = 7 (Read BE Negation) [0:2]

*/

writel(0x18683372, eim_reg + 0x00000008);

writel(0x00000068, eim_reg + 0x0000000C);

/*

* For EIM Write Configuration registers.

*

* CS0WCR1:

* Bit 31 30 29 28 27 26 25 24 23 22 21 20--19 18 17 16--15

* WAL WBED WWSC WADVA WADVN WBEA

* 1 1 01 1000 011 0--00 11--1

* Bit 14 13 12 11 10 9 8-- 7 6 5 4 3 2 1 0

* WBEN WEA WEN WCSA WCSN

* 111 111 1--11 100 110

* CS0WCR2:

* WBCDD = 0

*/

writel(0xd863ffe6, eim_reg + 0x00000010);

writel(0x00000000, eim_reg + 0x00000014);

printk("WEIM init end, CS0GCR1_is %x\n", readl(eim_reg));

iounmap(eim_reg);

iounmap(ccm_reg);

}3、probe函数修改

probe函数中主要针对添加了rst引脚和led引脚,其它未做改变。可以看到,probe函数中,申请了sja1000设备的总线资源,根据GPIO中断引脚号申请了终端,然后将platform设备注册到sja1000驱动中。

static int sp_probe(struct platform_device *pdev)

{

...

res_mem = platform_get_resource(pdev, IORESOURCE_MEM, 0);

if (!res_mem)

return -ENODEV;

if (!devm_request_mem_region(&pdev->dev, res_mem->start, resource_size(res_mem), DRV_NAME))

return -EBUSY;

addr = devm_ioremap_nocache(&pdev->dev, res_mem->start, resource_size(res_mem));

if (!addr)

return -ENOMEM;

if (of){

reset_pin = of_get_named_gpio(of, "rst-gpios", 0);

irq_pin = of_get_named_gpio(of, "int-gpios", 0);

led_pin = of_get_named_gpio(of, "led-gpios", 0);

irq = irq_of_parse_and_map(of, 0);

if(gpio_is_valid(reset_pin)) {

err = devm_gpio_request_one(&pdev->dev, reset_pin,

GPIOF_OUT_INIT_HIGH, "sja1000 reset");

if (err) {

dev_err(&pdev->dev,

"Failed to request GPIO %d as reset pin, error %d\n",

reset_pin, err);

}

}

if(gpio_is_valid(irq_pin)){

err = devm_gpio_request_one(&pdev->dev, irq_pin,

GPIOF_IN, "sja1000 int");

if (err) {

dev_err(&pdev->dev,

"Failed to request GPIO %d as irq pin, error %d\n",

irq_pin, err);

}

}

if(gpio_is_valid(led_pin)) {

err = devm_gpio_request_one(&pdev->dev, led_pin,

GPIOF_OUT_INIT_LOW, "sja1000 led");

if (err) {

dev_err(&pdev->dev,

"Failed to request GPIO %d as led pin, error %d\n",

irq_pin, err);

}

}

}else{

res_irq = platform_get_resource(pdev, IORESOURCE_IRQ, 0);

}

...

dev = alloc_sja1000dev(0);

...

priv = netdev_priv(dev);

if (res_irq) {

irq = res_irq->start;

priv->irq_flags = res_irq->flags & IRQF_TRIGGER_MASK;

if (res_irq->flags & IORESOURCE_IRQ_SHAREABLE)

priv->irq_flags |= IRQF_SHARED;

} else {

priv->irq_flags |= IRQF_TRIGGER_LOW;

}

dev->irq = irq;

priv->reg_base = addr;

priv->irq_pin = irq_pin;

priv->reset_pin = reset_pin;

priv->led_pin = led_pin;

priv->led_status = 0;

priv->wdataOffset = res_mem->start - 0x08000000; /* add write data offset */

if (of)

sp_populate_of(priv, of);

else

sp_populate(priv, pdata, res_mem->flags);

platform_set_drvdata(pdev, dev);

SET_NETDEV_DEV(dev, &pdev->dev);

err = register_sja1000dev(dev);

...

}4. read/write 地址偏移

由于使用的是DA1_8引脚(DA9_12充当了CS信号),其读写地址肯定不能直接在基地址上了。修改sja100_platform中的write8和read8函数,完成读写的地址偏移。

static u8 sp_read_reg8(const struct sja1000_priv *priv, int reg)

{

u16 data;

data = ioread16(priv->reg_base + reg*2);

return data>>1;

}

static void sp_write_reg8(const struct sja1000_priv *priv, int reg, u8 val)

{

u16 data=val;

data = data*2;

iowrite16(data + priv->wdataOffset, priv->reg_base + reg*2);

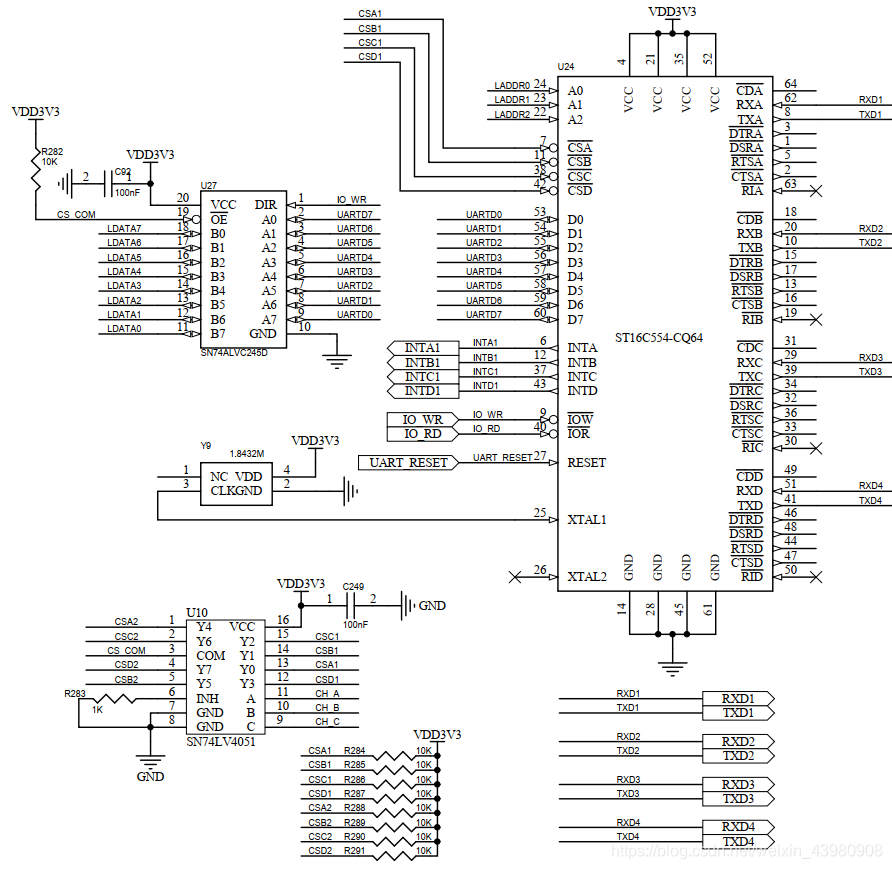

}最近做了一个项目使用的正点原子的imx6ull核心板平台,里面涉及到了有关于使用imx6ull的EIM接口进行外部串口扩展的部分,串口扩展芯片使用的是ST16C554这个芯片。这里针对这部分内容做一个记录和分享。

设备树部分

pinctrl_COM1_8: COM1_8 {

fsl,pins = <

MX6UL_PAD_LCD_DATA08__EIM_DATA00 0x10b1

MX6UL_PAD_LCD_DATA09__EIM_DATA01 0x10b1

MX6UL_PAD_LCD_DATA10__EIM_DATA02 0x10b1

MX6UL_PAD_LCD_DATA11__EIM_DATA03 0x10b1

MX6UL_PAD_LCD_DATA12__EIM_DATA04 0x10b1

MX6UL_PAD_LCD_DATA13__EIM_DATA05 0x10b1

MX6UL_PAD_LCD_DATA14__EIM_DATA06 0x10b1

MX6UL_PAD_LCD_DATA15__EIM_DATA07 0x10b1

MX6UL_PAD_CSI_PIXCLK__EIM_OE 0x10b1 /* IO_RD */

MX6UL_PAD_CSI_VSYNC__EIM_RW 0x10b1 /* IO_WR */

MX6UL_PAD_CSI_DATA00__EIM_AD00 0x10b1 /* A0 */

MX6UL_PAD_CSI_DATA01__EIM_AD01 0x10b1 /* A1 */

MX6UL_PAD_CSI_DATA02__EIM_AD02 0x10b1 /* A2 */

MX6UL_PAD_CSI_DATA03__EIM_AD03 0x10b1 /* A3 模拟开关选择 */

MX6UL_PAD_CSI_DATA04__EIM_AD04 0x10b1 /* A4 模拟开关选择 */

MX6UL_PAD_CSI_DATA05__EIM_AD05 0x10b1 /* A5 模拟开关选择 */

MX6UL_PAD_CSI_MCLK__EIM_CS0_B 0x10b1 /* CS0 8选1 */

MX6UL_PAD_LCD_DATA20__GPIO3_IO25 0x3000 /* INTA1 */

MX6UL_PAD_LCD_DATA19__GPIO3_IO24 0x3000 /* INTB1 */

MX6UL_PAD_LCD_DATA21__GPIO3_IO26 0x3000 /* INTC1 */

MX6UL_PAD_LCD_DATA18__GPIO3_IO23 0x3000 /* INTD1 */

MX6UL_PAD_LCD_DATA17__GPIO3_IO22 0x3000 /* INTA2 */

MX6UL_PAD_LCD_DATA16__GPIO3_IO21 0x3000 /* INTB2 */

MX6UL_PAD_LCD_DATA22__GPIO3_IO27 0x3000 /* INTC2 */

MX6UL_PAD_LCD_DATA23__GPIO3_IO28 0x3000 /* INTD2 */

MX6UL_PAD_GPIO1_IO05__GPIO1_IO05 0x10b1 /* UART_RESET */

>;

上面的是设备树的引脚属性设置部分。

&weim {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_COM1_8>;

#address-cells = <2>;

#size-cells = <1>;

fsl,weim-cs-gpr = <&gpr>;

ranges = <0 0 0x50000000 0x08000000>;

status = "okay";

st16c554@0,8 {

compatible = "st16c554";

reg = <0 0 0x08000000>;

fsl,weim-cs-timing = <0x00640081 0x00000001 0x1c022000

0x0000c000 0x1404a38e 0x00000000>;

};

};

上面的是设备树中关于eim接口的相关设置。这里主要说明一下fsl,weim-cs-timing属性,该属性就是设置eim通道的寄存器值的,imx6ull的eim接口根据cs计算一共4个通道,我这里通过ranges 设置只使用了通道0,fsl,weim-cs-timing的六个值就会设置为通道0的6个寄存器对应的值。设备树中的其他属性对应的意义可以参考linux的文档说明Documentation\devicetree\bindings\bus\imx-weim.txt,寄存器的具体含义参考imx6ull的参考文档即可。

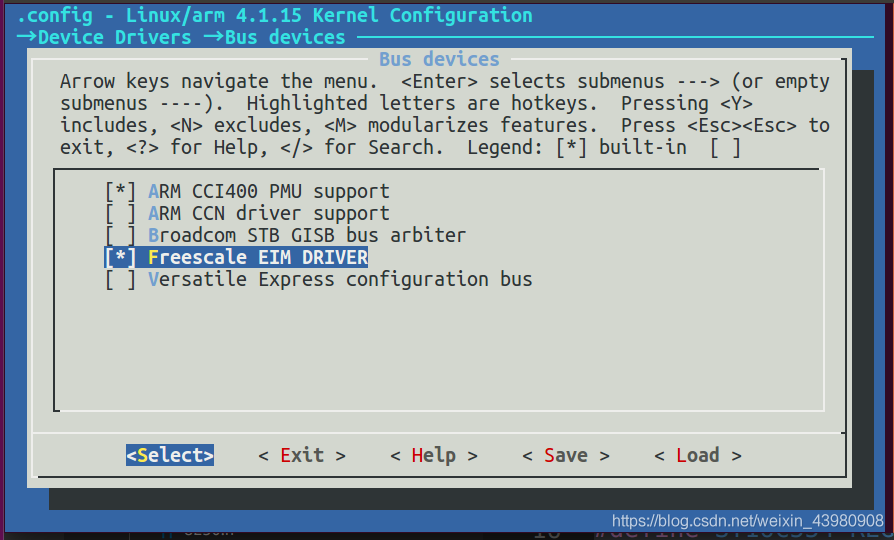

开启8250串口驱动,使用的端口数量的话根据自己的使用你情况进行配置即可,我这里用到8个所以设置8个。还有我发现一个奇怪的现象就是设置0个端口register at runtime时内核好像就会启动失败,控制台什么都不输出了,不知道是什么情况,总之设置时下面那个数字不要设置为0。

#include <linux/module.h>

#include <linux/init.h>

#include <linux/serial_8250.h>

#include <linux/platform_device.h>

#include <linux/kernel.h>

#include <linux/of_irq.h>

#include <linux/irq.h>

#include <linux/of_gpio.h>

#include <linux/delay.h>

#include <linux/gpio.h>

#include <asm/irq.h>

#include <asm/mach/map.h>

#include <asm/io.h>

#define ST16C554_REG_SIZE 0x08

#define IMX_GPIO_NR(bank, nr) (((bank) - 1) * 32 + (nr))

#define CS0_BASE 0x50000000

#define CSA1_BASE CS0_BASE

#define CSB1_BASE (CS0_BASE | 1 << 3) //A3 A4 A5作为8选1模拟开关选择线

#define CSC1_BASE (CS0_BASE | 2 << 3)

#define CSD1_BASE (CS0_BASE | 3 << 3)

#define CSA2_BASE (CS0_BASE | 4 << 3)

#define CSB2_BASE (CS0_BASE | 5 << 3)

#define CSC2_BASE (CS0_BASE | 6 << 3)

#define CSD2_BASE (CS0_BASE | 7 << 3)

/* 寄存器地址偏移定义 */

#define PORT_REG_RHR 0

#define PORT_REG_THR 0

#define PORT_REG_IER 1

#define PORT_REG_ISR 2

#define PORT_REG_FCR 2

#define PORT_REG_LCR 3

#define PORT_REG_MCR 4

#define PORT_REG_LSR 5

#define PORT_REG_MSR 6

#define PORT_REG_SPR 7

#define PORT_REG_DLL 0 //波特率设置寄存器

#define PORT_REG_DLM 1

#define PORT(_base,_irq) \

{ \

.type = PORT_16550A, \

.iobase = _base, \

.mapbase = _base, \

.irq = _irq, \

.irqflags = IRQF_TRIGGER_RISING, \

.uartclk = 1843200, \

.iotype = UPIO_MEM, \

.regshift = 0, \

.flags = UPF_BOOT_AUTOCONF | UPF_IOREMAP, \

}

#define ST16C554_INTA1 gpio_to_irq(IMX_GPIO_NR(3,25))

#define ST16C554_INTB1 gpio_to_irq(IMX_GPIO_NR(3,24))

#define ST16C554_INTC1 gpio_to_irq(IMX_GPIO_NR(3,26))

#define ST16C554_INTD1 gpio_to_irq(IMX_GPIO_NR(3,23))

#define ST16C554_INTA2 gpio_to_irq(IMX_GPIO_NR(3,22))

#define ST16C554_INTB2 gpio_to_irq(IMX_GPIO_NR(3,21))

#define ST16C554_INTC2 gpio_to_irq(IMX_GPIO_NR(3,27))

#define ST16C554_INTD2 gpio_to_irq(IMX_GPIO_NR(3,28))

static struct plat_serial8250_port exar_data[] = {

PORT(CSA1_BASE, 0),

PORT(CSB1_BASE, 0),

PORT(CSC1_BASE, 0),

PORT(CSD1_BASE, 0),

PORT(CSA2_BASE, 0),

PORT(CSB2_BASE, 0),

PORT(CSC2_BASE, 0),

PORT(CSD2_BASE, 0),

{ },

};

static struct platform_device exar_device = {

.name = "serial8250",

// .id = PLAT8250_DEV_EXAR_ST16C554,

.dev = {

.platform_data = exar_data,

},

};

int fsl8250_handle_irq(struct uart_port *port)

{

unsigned char lsr, orig_lsr;

unsigned long flags;

unsigned int iir;

struct uart_8250_port *up = up_to_u8250p(port);

// printk("irq = %d ", port->irq);

spin_lock_irqsave(&up->port.lock, flags);

iir = port->serial_in(port, PORT_REG_ISR);

if (iir & 0x01) {

spin_unlock_irqrestore(&up->port.lock, flags);

return 0;

}

/* This is the WAR; if last event was BRK, then read and return */

if (unlikely(up->lsr_saved_flags & 0x10)) {

up->lsr_saved_flags &= ~0x10;

port->serial_in(port, PORT_REG_RHR);

spin_unlock_irqrestore(&up->port.lock, flags);

return 1;

}

lsr = orig_lsr = up->port.serial_in(&up->port, PORT_REG_LSR);

if (lsr & 0x01)

lsr = serial8250_rx_chars(up, lsr);

serial8250_modem_status(up);

if (lsr & 0x20)

serial8250_tx_chars(up);

up->lsr_saved_flags = orig_lsr;

spin_unlock_irqrestore(&up->port.lock, flags);

return 1;

}

static int __init my_serial_init(void)

{

int ret;

int rst_io;

exar_data[0].irq = ST16C554_INTA1;

exar_data[1].irq = ST16C554_INTB1;

exar_data[2].irq = ST16C554_INTC1;

exar_data[3].irq = ST16C554_INTD1;

exar_data[4].irq = ST16C554_INTA2;

exar_data[5].irq = ST16C554_INTB2;

exar_data[6].irq = ST16C554_INTC2;

exar_data[7].irq = ST16C554_INTD2;

exar_data[0].handle_irq = fsl8250_handle_irq;

exar_data[1].handle_irq = fsl8250_handle_irq;

exar_data[2].handle_irq = fsl8250_handle_irq;

exar_data[3].handle_irq = fsl8250_handle_irq;

exar_data[4].handle_irq = fsl8250_handle_irq;

exar_data[5].handle_irq = fsl8250_handle_irq;

exar_data[6].handle_irq = fsl8250_handle_irq;

exar_data[7].handle_irq = fsl8250_handle_irq;

rst_io = IMX_GPIO_NR(1,5); //获得io编号

ret = gpio_direction_output(rst_io, 0); //复位

ret = gpio_direction_output(rst_io, 1);

if (ret < 0) {

printk("%s rst_io ouput error\n", __func__);

}

udelay(10); //延时10us

gpio_set_value(rst_io, 0);

udelay(1000); //延时1000us

return platform_device_register(&exar_device);

}

static void __exit my_serial_exit(void)

{

printk("unregister st16c554_driver\n");

platform_device_unregister(&exar_device);

}

module_init(my_serial_init);

module_exit(my_serial_exit);

MODULE_LICENSE("GPL");

MODULE_AUTHOR("ljf");

PORT里面的参数我捡几个主要的进行说明一下,mapbase和iobase都是实际的物理地址,这个和你的EIM总线配置以及硬件连接有关。irq就是中断号,uartclk就是外接的时钟频率我接的是1.8432M的时钟就设置为1843200,串口的波特率最大就是clk/16,iotype设置为UPIO_MEM表示8位的内存地址,regshift表示地址偏移由于我是A0对应的ST16C554的A0所以设置为0表示没有偏移,UPF_IOREMAP表示地址需要映射到虚拟地址进行访问。

然后在init函数中申请中断号,设置handle_irq,进行芯片复位,最后将其注册成platform设备。然后就会和8250驱动匹配上进行8250驱动的一套流程,这里就不分析了。handle_irq函数可以参考8250_fsl.c和8250_core.c文件,里面都有相应的示例。

虽然驱动写完了但是还是不能直接使用,使用之前还需要开启EIM的时钟,虽然设备树里面设置了status的属性为okay但是eim的时钟却没有被开启,而且我试了直接在上面驱动中的init函数里设置CCM_CCGR6寄存器的bit10-11位,但是没用,只能在内核初始化完成之后再开启对应的时钟。于是我就又写了一个开启时钟的驱动。

static int __init st16c554_cmd_init(void)

{

void __iomem *ccm_ccgr6 = ioremap(CCM_BASE_ADDR + 0x80, 4);

unsigned int reg;

/* CLKCTL_CCGR6: Set emi_slow_clock to be on in all modes */

reg = readl(ccm_ccgr6);

reg |= 0x00000C00;

writel(reg, ccm_ccgr6);

reg = readl(ccm_ccgr6);

iounmap(ccm_ccgr6);

return 0;

}

static void __exit st16c554_cmd_exit(void)

{

}

module_init(st16c554_cmd_init);

module_exit(st16c554_cmd_exit);

MODULE_LICENSE("GPL");

驱动里面直接就是映射寄存器地址然后设置值,其他的什么都不做。这个驱动会在根文件系统加载之后被调用自动开启eim总线的时钟。

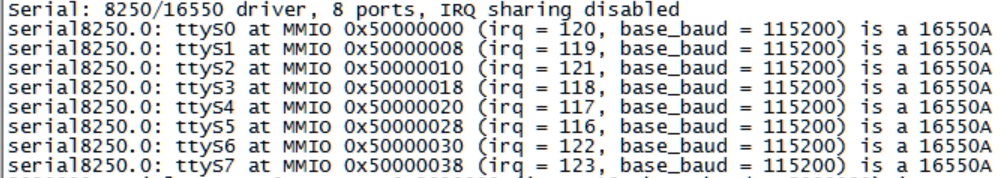

将驱动编译进内核里面,用新的内核进行启动如果驱动加载成功之后内核启动就会打印出相应的信息来,如上图所示。查看/dev目录可以看到已经有ttyS0-7这几个设备节点了。

1.1 Linux下RTC时间的读写分析

1.1.1 系统时间与RTC实时时钟时间

Linux系统下包含两个时间:系统时间和RTC时间。

系统时间:是由主芯片的定时器进行维护的时间,一般情况下都会选择芯片上最高精度的定时器作为系统时间的定时基准,以避免在系统运行较长时间后出现大的时间偏移。特点是掉电后不保存。

RTC时间:是指系统中包含的RTC芯片内部所维护的时间。RTC芯片都有电池+系统电源的双重供电机制,在系统正常工作时由系统供电,在系统掉电后由电池进行供电。因此系统电源掉电后RTC时间仍然能够正常运行。

每次Linux系统启动后在启动过程中会检测和挂载RTC驱动,在挂载后会自动从RTC芯片中读取时间并设置到系统时间中去。此后如果没有显式的通过命令去控制RTC的读写操作,系统将不会再从RTC中去获取或者同步设置时间。

linux命令中的date和time等命令都是用来设置系统时间的,而hwclock命令是用来设置和读写RTC时间的。

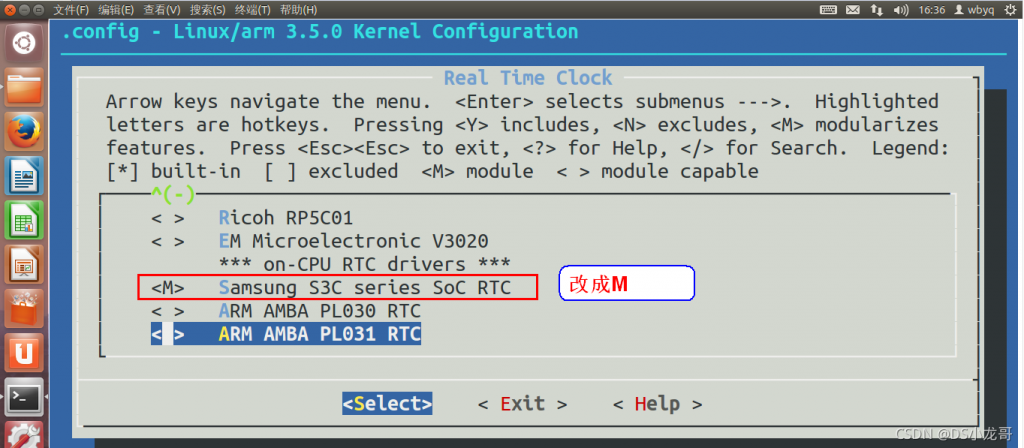

1.1.2 Linux内核RTC实时时钟配置查看与选择:

进入到内核根目录下,输入: make menuconfig 进入到内核配置菜单:

Device Drivers --->

[*] Real Time Clock --->

--- Real Time Clock │ │

│ │ [*] Set system time from RTC on startup and resume │ │

│ │ (rtc0) RTC used to set the system time │ │

│ │ [ ] RTC debug support │ │

│ │ *** RTC interfaces *** │ │

│ │ [*] /sys/class/rtc/rtcN (sysfs)

[*] /proc/driver/rtc (procfs for rtc0) │ │

│ │ [*] /dev/rtcN (character devices) │ │

│ │ [ ] RTC UIE emulation on dev interface │ │

│ │ < > Test driver/device │ │

│ │ *** I2C RTC drivers *** │ │

│ │ < > Dallas/Maxim DS1307/37/38/39/40, ST M41T00, EPSON RX-8025

< > Dallas/Maxim DS1374 │ │

│ │ < > Dallas/Maxim DS1672 │ │

│ │ < > Dallas/Maxim DS3232 │ │

│ │ < > Maxim MAX6900 │ │

│ │ < > Ricoh R2025S/D, RS5C372A/B, RV5C386, RV5C387A

< > Intersil ISL1208 │ │

│ │ < > Intersil ISL12022 │ │

│ │ < > Xicor/Intersil X1205 │ │

│ │ < > Philips PCF8563/Epson RTC8564 │ │

│ │ < > Philips PCF8583 │ │

│ │ < > ST M41T62/65/M41T80/81/82/83/84/85/87

< > TI BQ32000 │ │

│ │ < > Seiko Instruments S-35390A │ │

│ │ < > Ramtron FM3130 │ │

│ │ < > Epson RX-8581 │ │

│ │ < > Epson RX-8025SA/NB │ │

│ │ < > EM Microelectronic EM3027

< > Micro Crystal RTC │ │

│ │ *** SPI RTC drivers *** │ │

│ │ < > ST M41T93 │ │

│ │ < > ST M41T94 │ │

│ │ < > Dallas/Maxim DS1305/DS1306 │ │

│ │ < > Dallas/Maxim DS1390/93/94

*** Platform RTC drivers *** │ │

│ │ < > PC-style 'CMOS' │ │

│ │ < > Dallas DS1286 │ │

│ │ < > Dallas DS1511 │ │

│ │ < > Maxim/Dallas DS1553

*** on-CPU RTC drivers *** │ │

│ │ <*> Samsung S3C series SoC RTC │ │

│ │ < > ARM AMBA PL030 RTC │ │

│ │ < > ARM AMBA PL031 RTC │ │ 根据内核的配置得知3个信息(红色选中的配置选项):

(rtc0表示/dev下第一个rtc驱动,如果安装了第二个RTC驱动,就以rtc1表示,依次类推)

驱动源码\linux-3.5\drivers\rtc\ rtc-s3c.c是三星公司编写的RTC驱动。

1.1.3 date命令使用介绍

date是用来显示或设定系统的日期与时间的命令。

命令使用格式: date [参数]… [+格式]

命令可以的参数如下:

使用示例: date '+%A'

必要参数:

%H 小时(以00-23来表示)。

%I 小时(以01-12来表示)。

%K 小时(以0-23来表示)。

%l 小时(以0-12来表示)。

%M 分钟(以00-59来表示)。

%P AM或PM。

%r 时间(含时分秒,小时以12小时AM/PM来表示)。

%s 总秒数。起算时间为1970-01-01 00:00:00 UTC。

%S 秒(以本地的惯用法来表示)。

%T 时间(含时分秒,小时以24小时制来表示)。

%X 时间(以本地的惯用法来表示)。

%Z 市区。

%a 星期的缩写。

%A 星期的完整名称。

%b 月份英文名的缩写。

%B 月份的完整英文名称。

%c 日期与时间。只输入date指令也会显示同样的结果。

%d 日期(以01-31来表示)。

%D 日期(含年月日)。

%j 该年中的第几天。

%m 月份(以01-12来表示)。

%U 该年中的周数。

%w 该周的天数,0代表周日,1代表周一,异词类推。

%x 日期(以本地的惯用法来表示)。

%y 年份(以00-99来表示)。

%Y 年份(以四位数来表示)。

%n 在显示时,插入新的一行。

%t 在显示时,插入tab。

MM 月份(必要)

DD 日期(必要)

hh 小时(必要)

mm 分钟(必要)

ss 秒(选择性)

选择参数:

-d<字符串> 显示字符串所指的日期与时间。字符串前后必须加上双引号。

-s<字符串> 根据字符串来设置日期与时间。字符串前后必须加上双引号。

-u 显示GMT。

--help 在线帮助。

--version 显示版本信息系统时间的方式

[root@XiaoLong /]# date -s "2018-07-28 14:21:22" //设置全部日期与时间

[root@XiaoLong /]# date -s "14:30:22" //只设置时间

[root@XiaoLong /]# date -s "2017-07-28" //设置日期,时间默认为00:00:00格式示例

[root@XiaoLong /]# date -r app // -r选项可以打印出指定文件的最后修改时间

Fri Apr 29 05:17:34 UTC 2016

[root@XiaoLong /]# date -d 23:39:00 //打印出指定格式时间(只是打印效果没有其他效果)

Sat Apr 30 23:39:00 UTC 2016

[root@XiaoLong /]# date -s 12:20:30 //设置系统时间为12点20分30秒

Sat Apr 30 12:20:30 UTC 2016

[root@XiaoLong /]# date -s 2016.04.30-23:20:10 //设置系统时间为2016年4月30日23点20分10秒

Sat Apr 30 23:20:10 UTC 20161. 将RTC时间同步到系统时间

[root@XiaoLong /]# hwclock -s为了在启动时自动执行RTC时间同步到系统时间,可以把hwclock -s命令加入到profile或者rcS文件中。

2. 获取显示RTC时间

[root@XiaoLong /]# hwclock -r

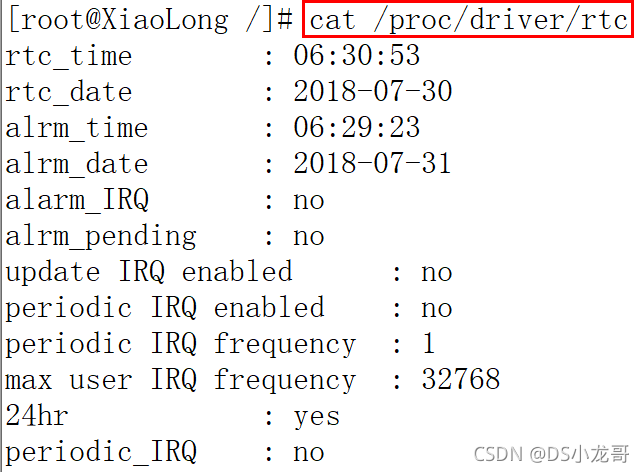

Sun May 1 00:09:36 2016 0.000000 seconds[root@XiaoLong /]# hwclock -w4. 查看RTC的信息

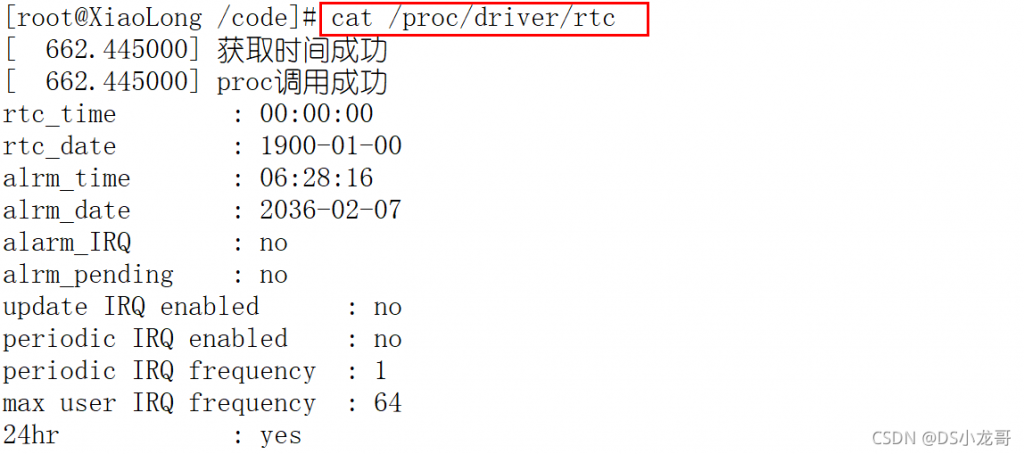

[root@XiaoLong /]# cat /proc/driver/rtc

rtc_time : 00:09:27

rtc_date : 2016-05-01

alrm_time : 23:24:07

alrm_date : 2016-05-01

alarm_IRQ : no

alrm_pending : no

update IRQ enabled : no

periodic IRQ enabled : no

periodic IRQ frequency : 1

max user IRQ frequency : 32768

24hr : yes

periodic_IRQ : no1.2 Linux内核RTC子系统结构

1.2.1 RTC框架相关的核心文件

Linux内核源码自带的RTC驱动代码存放位置:

\linux-3.5\drivers\rtc\目录下全是RTC驱动示例代码

其中:rtc-s3c.c 是三星公司编写的RTC驱动1. RTC框架注册函数

struct rtc_device *rtc_device_register(

const char *name, //RTC时钟名称

struct device *dev, //设备指针。该指针需要需要通过平台设备获取。

const struct rtc_class_ops *ops, //rtc文件操作集合

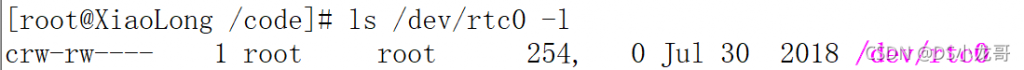

struct module *owner) //驱动所有者。填: THIS_MODULE使用示例: rtc_device_register(“tiny4412_rtc”,&pdev->dev, &tiny4412_rtcops,THIS_MODULE);

使用rtc_device_register函数注册成功之后,在/dev/下可以看到rtcx的设备节点(x是rtc的顺序编号)。

2. RTC框架注销函数

void rtc_device_unregister(struct rtc_device *rtc)经过RTC注册函数形参分析,RTC子系统的注册需要通过平台设备框架完成,在平台设备的驱动端的probe函数里进行rtc注册,remove函数里进行注销,在rtc设备端向驱动端传递RTC硬件需要的一些信息。

1.2.3 文件操作集合接口

rtc_class_ops 这个结构是RTC驱动程序要实现的基本操作函数。驱动程序通过初始化这样一个结构,将自己实现的函数与RTC核心联系起来。这里面的大部分函数都要驱动程序来实现。而且这些函数都是操作底层硬件的,属于最底层的函数。这个驱动接口与应用层的hwclock命令关联在一起,可以通过hwclock命令调用底层RTC这些函数。

struct rtc_class_ops {

int (*open)(struct device *); //打开

void (*release)(struct device *);

int (*ioctl)(struct device *, unsigned int, unsigned long); /*ioctl函数*/

int (*read_time)(struct device *, struct rtc_time *); //读取时间

int (*set_time)(struct device *, struct rtc_time *); //设置时间

int (*read_alarm)(struct device *, struct rtc_wkalrm *); //读取闹钟

int (*set_alarm)(struct device *, struct rtc_wkalrm *); //设置闹钟

int (*proc)(struct device *, struct seq_file *); //proc接口

int (*set_mmss)(struct device *, unsigned long secs); //设置秒单位

int (*read_callback)(struct device *, int data); //回调函数

int (*alarm_irq_enable)(struct device *, unsigned int enabled); //闹钟中断使能

};RTC子系统里驱动一般只需要实现设置时间和获取时间的函数接口即可,用户可以在应用层通过ioctl函数传入对应的命令调用驱动层的接口,实现时间获取与设置。

常用的两个命令:

#define RTC_RD_TIME _IOR(RTC_MAGIC, 0x09, struct rtc_time) /* Read RTC time. */

#define RTC_SET_TIME _IOW(RTC_MAGIC, 0x0a, struct rtc_time) /* Set RTC time. */

//支持的全部命令 在interface.c文件中有使用范例。 这些命令在用户自己写应用层代码时可以用到

RTC_ALM_READ rtc_read_alarm 读取闹钟时间

RTC_ALM_SET rtc_set_alarm 设置闹钟时间

RTC_RD_TIME rtc_read_time 读取时间与日期

RTC_SET_TIME rtc_set_time 设置时间与日期

RTC_PIE_ON RTC_PIE_OFF rtc_irq_set_state 开关RTC全局中断的函数

RTC_AIE_ON RTC_AIE_OFF rtc_alarm_irq_enable 使能禁止RTC闹钟中断

RTC_UIE_OFF RTC_UIE_ON rtc_update_irq_enable 使能禁止RTC更新中断

RTC_IRQP_SET rtc_irq_set_freq 设置中断的频率rtc_time代表了RTC记录的时间与日期,从RTC设备读回的时间和日期就保存在这个结构体中。

struct rtc_time {

int tm_sec; //秒

int tm_min; //分钟

int tm_hour; //小时

int tm_mday; //天

int tm_mon; //月

int tm_year; //年

int tm_wday; //一周中的某一天

int tm_yday; //一年中的某一天

int tm_isdst; //夏令时有效

};1.2.5 闹钟结构

struct rtc_wkalrm {

unsigned char enabled; /* 闹钟使能开关 0 = alarm disabled, 1 = alarm enabled */

unsigned char pending;

/* 闹钟信号处理状态 0 = alarm not pending 未产生, 1 = alarm pending 产生了闹钟信号*/

struct rtc_time time; /* 闹钟设置的时间 */

};要测试自己的编写的RTC驱动,提前需要将内核自带的RTC驱动先去除掉,再重新编译烧写内核,再安装测试。

以tiny4412开发板为例,去除掉自带的rtc驱动。

1. 进入到内核配置菜单: make menuconfig

Device Drivers --->

[*] Real Time Clock --->

2. 重新编译内核,再重新烧写内核到SD或者EMMC:

[root@wbyq boot]# ./123.sh

记录了9288+1 的读入

记录了9288+1 的写出

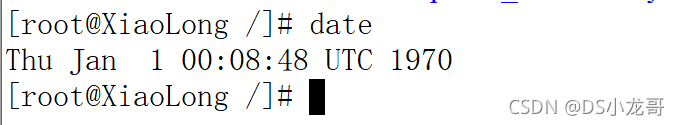

4755752字节(4.8 MB)已复制,33.2798 秒,143 kB/秒默认没有RTC驱动的情况下,获取系统时间是从1970年开始的:

以下代码只是演示了RTC驱动的注册框架。

1. RTC设备端代码:

#include "linux/module.h"

#include "linux/init.h"

#include <linux/platform_device.h>

/*

* device 设备端

*/

//释放平台总线

static void pdev_release(struct device *dev)

{

printk("rtc_pdev:the rtc_pdev is close!!!\n");

}

/*设备端结构体*/

struct platform_device rtc_pdev= /*设备结构体,设备名字很重要!*/

{

.name = "tiny4412rtc", /*设备名*/

.id = -1, /*-1表示创建成功后这边设备的名字就叫myled,若该值为0,1则设备名是myled.0,myled.1...*/

.dev = /*驱动卸载时调用*/

{

.release = pdev_release,/*释放资源*/

},

};

/*平台设备端入口函数*/

static int __init plat_dev_init(void)

{

platform_device_register(&rtc_pdev);/*注册平台设备端*/

return 0;

}

/*平台设备端出口函数*/

static void __exit plat_dev_exit(void)

{

platform_device_unregister(&rtc_pdev);/*注销平台设备端*/

}

module_init(plat_dev_init);

module_exit(plat_dev_exit);

MODULE_LICENSE("GPL");2. RTC驱动端代码

#include <linux/module.h> /*驱动模块相关*/

#include <linux/init.h>

#include <linux/fs.h> /*文件操作集合*/

#include <linux/cdev.h>

#include <linux/device.h>

#include <linux/miscdevice.h>

#include <asm/io.h>

#include <asm/uaccess.h>

#include <linux/interrupt.h> /*中断相关头文件*/

#include <linux/irq.h> /*中断相关头文件*/

#include <linux/gpio.h> /*硬件相关->定义了寄存器名字与地址*/

#include <linux/wait.h>

#include <linux/sched.h>

#include <linux/timer.h> /*内核定时器*/

#include <asm-generic/poll.h>

#include <linux/poll.h> /* poll机制*/

#include <linux/platform_device.h> /* 平台设备驱动相关头文件*/

#include <linux/rtc.h>

static int tiny4412_rtc_gettime(struct device *dev, struct rtc_time *rtc_tm)

{

printk("获取时间成功\n");

return 0;

}

static int tiny4412_rtc_settime(struct device *dev, struct rtc_time *tm)

{

printk("设置时间成功\n");

return 0;

}

static int tiny4412_rtc_getalarm(struct device *dev, struct rtc_wkalrm *alrm)

{

printk("getalarm调用成功\n");

return 0;

}

static int tiny4412_rtc_setalarm(struct device *dev, struct rtc_wkalrm *alrm)

{

printk("getalarm调用成功\n");

return 0;

}

static int tiny4412_rtc_proc(struct device *dev, struct seq_file *seq)

{

printk("proc调用成功\n");

return 0;

}

static int tiny4412_rtc_alarm_irq_enable(struct device *dev, unsigned int enabled)

{

printk("alarm_irq_enable调用成功\n");

return 0;

}

static int tiny4412_rtc_ioctl(struct device *dev, unsigned int cmd,unsigned long arg)

{

printk("ioctl调用成功\n");

return 0;

}

/*RTC文件操作*/

static const struct rtc_class_ops tiny4412_rtcops = {

.read_time = tiny4412_rtc_gettime,

.set_time = tiny4412_rtc_settime,

.read_alarm = tiny4412_rtc_getalarm,

.set_alarm = tiny4412_rtc_setalarm,

.proc = tiny4412_rtc_proc,

.alarm_irq_enable = tiny4412_rtc_alarm_irq_enable,

.ioctl = tiny4412_rtc_ioctl,

};

struct rtc_device *rtc=NULL;

/*当设备匹配成功执行的函数-资源探查函数*/

static int drv_probe(struct platform_device *pdev)

{

rtc = rtc_device_register("tiny4412_rtc",&pdev->dev, &tiny4412_rtcops,THIS_MODULE);

if(rtc==NULL)

printk("RTC驱动注册失败\n");

else

{

printk("RTC驱动注册成功\n");

}

return 0;

}

static int drv_remove(struct platform_device *dev)/*当设备卸载后调用这条函数*/

{

rtc_device_unregister(rtc);

printk("RTC驱动卸载成功\n");

return 0;

}

/*平台设备驱动端结构体-包含和probe匹配的设备名字*/

struct platform_driver drv=

{

.probe = drv_probe, /*需要创建一个probe函数,这个函数是对设备进行操作*/

.remove = drv_remove, /*创建一个remove函数,用于设备退出*/

.driver =

{

.name = "tiny4412rtc", /*设备名称,用来与设备端匹配(非常重要)*/

},

};

/*平台驱动端的入口函数*/

static int __init plat_drv_init(void)

{

platform_driver_register(&drv);/*注册平台驱动*/

return 0;

}

/*平台驱动端的出口函数*/

static void __exit plat_drv_exit(void)

{

platform_driver_unregister(&drv);/*释放平台驱动*/

}

module_init(plat_drv_init); /*驱动模块的入口*/

module_exit(plat_drv_exit); /*驱动模块的出口*/

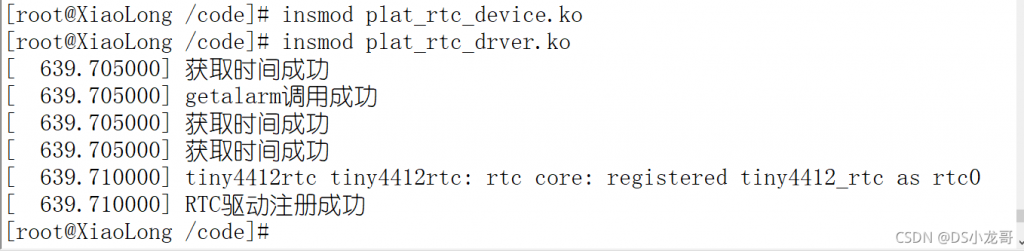

MODULE_LICENSE("GPL"); /*驱动的许可证-声明*/3. 安装RTC驱动

4. 查看生成的RTC的设备节点

5. 查看rtc信息

查看/proc/driver/rtc文件时,底层驱动函数接口也相继被调用,只不过刚才写的RTC驱动没有完善,所以获取的信息不正确,是默认值。

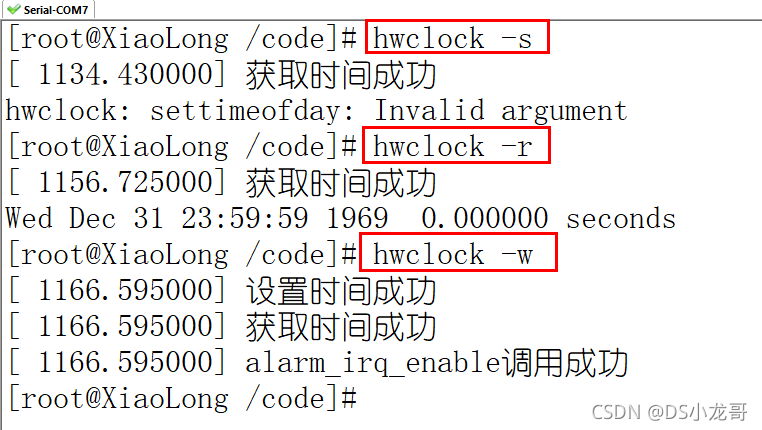

6. 设置RTC时间相关的命令测试

通过命令测试,设置时间和获取时间都调用了底层的RTC函数接口,剩下的工作就是完善驱动代码了。

1.3.3 完善RTC驱动

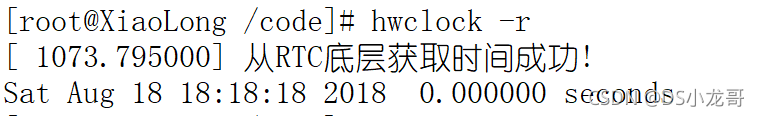

上一步完成了RTC驱动代码框架编写,这一步就先不添加RTC硬件代码,使用软件方式模拟时间传递给应用层。

注意: 内核里RTC时间换算的时间是从: 1900年开始计算的,月份是从0开始的。

在给rtc结构赋值时,在正常的年份上需要减去1900,月份再减去1

赋值示例:

//此函数可以通过应用层的ioctl的RTC_RD_TIME命令进行调用

static int tiny4412_rtc_gettime(struct device *dev, struct rtc_time *rtc_tm)

{

rtc_tm->tm_year=2018-1900; //年

rtc_tm->tm_mon=8-1; //月

rtc_tm->tm_mday=18; //日

rtc_tm->tm_hour=18; //时

rtc_tm->tm_min=18; //分

rtc_tm->tm_sec=18;//秒

printk("从RTC底层获取时间成功!\n");

return 0;

}应用层获取的时间如下:

完善过后的RTC设备驱动端代码

#include <linux/module.h> /*驱动模块相关*/

#include <linux/init.h>

#include <linux/fs.h> /*文件操作集合*/

#include <linux/cdev.h>

#include <linux/device.h>

#include <linux/miscdevice.h>

#include <asm/io.h>

#include <asm/uaccess.h>

#include <linux/interrupt.h> /*中断相关头文件*/

#include <linux/irq.h> /*中断相关头文件*/

#include <linux/gpio.h> /*硬件相关->定义了寄存器名字与地址*/

#include <linux/wait.h>

#include <linux/sched.h>

#include <linux/timer.h> /*内核定时器*/

#include <asm-generic/poll.h>

#include <linux/poll.h> /* poll机制*/

#include <linux/platform_device.h> /* 平台设备驱动相关头文件*/

#include <linux/rtc.h>

//此函数可以通过应用层的ioctl的RTC_RD_TIME命令进行调用

static int tiny4412_rtc_gettime(struct device *dev, struct rtc_time *rtc_tm)

{

rtc_tm->tm_year=2018-1900; //年

rtc_tm->tm_mon=8-1; //月

rtc_tm->tm_mday=18; //日

rtc_tm->tm_hour=18; //时

rtc_tm->tm_min=18; //分

rtc_tm->tm_sec=18;//秒

printk("从RTC底层获取时间成功!\n");

return 0;

}

//此函数可以通过应用层的ioctl的RTC_SET_TIME命令进行调用

static int tiny4412_rtc_settime(struct device *dev, struct rtc_time *tm)

{

printk("RTC收到的时间为:%d-%d-%d %d-%d-%d\n",1900 + tm->tm_year, tm->tm_mon, tm->tm_mday,

tm->tm_hour, tm->tm_min, tm->tm_sec);

return 0;

}

//获取闹钟时间

static int tiny4412_rtc_getalarm(struct device *dev, struct rtc_wkalrm *alrm)

{

alrm->enabled=0; //默认闹钟处于关闭状态

alrm->time.tm_year=2018-1900; //年

alrm->time.tm_mon=8-1; //月

alrm->time.tm_mday=18; //日

alrm->time.tm_hour=18; //时

alrm->time.tm_min=18; //分

alrm->time.tm_sec=18; //秒

printk("从RTC底层获取闹钟时间成功!\n");

return 0;

}

//设置闹钟时间

static int tiny4412_rtc_setalarm(struct device *dev, struct rtc_wkalrm *alrm)

{

printk("RTC闹钟设置成功\n");

return 0;

}

//proc接口调用

static int tiny4412_rtc_proc(struct device *dev, struct seq_file *seq)

{

printk("proc调用成功\n");

return 0;

}

//闹钟中断使能

static int tiny4412_rtc_alarm_irq_enable(struct device *dev, unsigned int enabled)

{

printk("alarm_irq_enable调用成功\n");

return 0;

}

//可以实现用户自定义的命令

static int tiny4412_rtc_ioctl(struct device *dev, unsigned int cmd,unsigned long arg)

{

printk("ioctl调用成功\n");

return 0;

}

/*RTC文件操作*/

static const struct rtc_class_ops tiny4412_rtcops = {

.read_time = tiny4412_rtc_gettime,

.set_time = tiny4412_rtc_settime,

.read_alarm = tiny4412_rtc_getalarm,

.set_alarm = tiny4412_rtc_setalarm,

.proc = tiny4412_rtc_proc,

.alarm_irq_enable = tiny4412_rtc_alarm_irq_enable,

.ioctl = tiny4412_rtc_ioctl,

};

struct rtc_device *rtc=NULL;

/*当设备匹配成功执行的函数-资源探查函数*/

static int drv_probe(struct platform_device *pdev)

{

rtc = rtc_device_register("tiny4412_rtc",&pdev->dev, &tiny4412_rtcops,THIS_MODULE);

if(rtc==NULL)

printk("RTC驱动注册失败\n");

else

{

printk("RTC驱动注册成功\n");

}

return 0;

}

static int drv_remove(struct platform_device *dev)/*当设备卸载后调用这条函数*/

{

rtc_device_unregister(rtc);

printk("RTC驱动卸载成功\n");

return 0;

}

/*平台设备驱动端结构体-包含和probe匹配的设备名字*/

struct platform_driver drv=

{

.probe = drv_probe, /*需要创建一个probe函数,这个函数是对设备进行操作*/

.remove = drv_remove, /*创建一个remove函数,用于设备退出*/

.driver =

{

.name = "tiny4412rtc", /*设备名称,用来与设备端匹配(非常重要)*/

},

};

/*平台驱动端的入口函数*/

static int __init plat_drv_init(void)

{

platform_driver_register(&drv);/*注册平台驱动*/

return 0;

}

/*平台驱动端的出口函数*/

static void __exit plat_drv_exit(void)

{

platform_driver_unregister(&drv);/*释放平台驱动*/

}

module_init(plat_drv_init); /*驱动模块的入口*/

module_exit(plat_drv_exit); /*驱动模块的出口*/

MODULE_LICENSE("GPL"); /*驱动的许可证-声明*/安装测试结果:

[root@XiaoLong /code]# date

Thu Jan 1 00:00:13 UTC 1970

[root@XiaoLong /code]# insmod plat_rtc_device.ko

[root@XiaoLong /code]# insmod plat_rtc_drver.ko

[ 24.350000] 从RTC底层获取时间成功!

[ 24.350000] 从RTC底层获取闹钟时间成功!

[ 24.350000] 从RTC底层获取时间成功!

[ 24.350000] tiny4412rtc tiny4412rtc: rtc core: registered tiny4412_rtc as rtc0

[ 24.350000] RTC驱动注册成功

[root@XiaoLong /code]# cat /proc/driver/rtc

[ 37.085000] 从RTC底层获取时间成功!

[ 37.085000] proc调用成功

rtc_time : 18:18:18

rtc_date : 2018-08-18

alrm_time : 18:18:18

alrm_date : 2018-08-18

alarm_IRQ : no

alrm_pending : no

update IRQ enabled : no

periodic IRQ enabled : no

periodic IRQ frequency : 1

max user IRQ frequency : 64

24hr : yes

[root@XiaoLong /code]#

[root@XiaoLong /code]# hwclock -s

[ 58.600000] 从RTC底层获取时间成功!

[root@XiaoLong /code]# hwclock -r

[ 61.020000] 从RTC底层获取时间成功!

Sat Aug 18 18:18:18 2018 0.000000 seconds

[root@XiaoLong /code]# hwclock -w

[ 62.920000] RTC收到的时间为:2018-7-18 18-18-22

[ 62.920000] 从RTC底层获取时间成功!

[ 62.920000] alarm_irq_enable调用成功

[root@XiaoLong /code]# date

Sat Aug 18 18:18:24 UTC 20181.3.4 RTC应用层代码

应用层想要与RTC驱动交互,可以使用ioctl函数特定的一些命令进行。

RTC子系统常用的ioctl命令如下:

//支持的全部命令 在interface.c文件中有使用范例。 这些命令在用户自己写应用层代码时可以用到

RTC_ALM_READ rtc_read_alarm 读取闹钟时间

RTC_ALM_SET rtc_set_alarm 设置闹钟时间

RTC_RD_TIME rtc_read_time 读取时间与日期

RTC_SET_TIME rtc_set_time 设置时间与日期

RTC_PIE_ON RTC_PIE_OFF rtc_irq_set_state 开关RTC全局中断的函数

RTC_AIE_ON RTC_AIE_OFF rtc_alarm_irq_enable 使能禁止RTC闹钟中断

RTC_UIE_OFF RTC_UIE_ON rtc_update_irq_enable 使能禁止RTC更新中断

RTC_IRQP_SET rtc_irq_set_freq 设置中断的频率示例代码:

#include <stdio.h>

#include <sys/types.h>

#include <sys/stat.h>

#include <fcntl.h>

#include <sys/ioctl.h>

#include <linux/rtc.h>

struct rtc_time time; //保存时间值

int main(int argc,char **argv)

{

if(argc!=2)

{

printf("传参格式:/dev/rtc\r\n");

return;

}

int fd=open(argv[1],O_RDWR); // 2==O_RDWR

if(fd<0)

{

printf("驱动设备文件打开失败!\r\n");

return 0;

}

time.tm_year=2017;

time.tm_mon=10;

time.tm_mday=13;

time.tm_hour=21;

time.tm_min=10;

time.tm_sec=10;

//注意:年月日必须填写正常,否则会导致底层函数无法调用成功

ioctl(fd,RTC_SET_TIME,&time); //底层自己实现了ioctl函数,设置RTC时间

while(1)

{

ioctl(fd,RTC_RD_TIME,&time);

printf("%d-%d-%d %d:%d:%d\r\n",time.tm_year,time.tm_mon,time.tm_mday,time.tm_hour,time.tm_min,time.tm_sec);

sleep(1);

}

}硬件上有些RTC实时时钟设置只计算秒数,不提供年月日时分秒格式的时间设置,这时候就需要自己对标准时间进行转换。

将标准时间转为秒单位时间:

/*

* 自01-01-1970就是将公历日期转换为秒。

*/

int rtc_tm_to_time(struct rtc_time *tm, unsigned long *time)

{

*time = mktime(tm->tm_year + 1900, tm->tm_mon + 1, tm->tm_mday,

tm->tm_hour, tm->tm_min, tm->tm_sec);

return 0;

}上面代码都是模拟时钟,学习RTC框架的用法,下面的的代码就加入了实际的RTC硬件,实现完整的RTC计时。

DS1302驱动端代码:

#include <linux/module.h> /*驱动模块相关*/

#include <linux/init.h>

#include <linux/fs.h> /*文件操作集合*/

#include <linux/cdev.h>

#include <linux/device.h>

#include <linux/miscdevice.h>

#include <asm/io.h>

#include <asm/uaccess.h>

#include <linux/interrupt.h> /*中断相关头文件*/

#include <linux/irq.h> /*中断相关头文件*/

#include <linux/gpio.h> /*硬件相关->定义了寄存器名字与地址*/

#include <linux/wait.h>

#include <linux/sched.h>

#include <linux/timer.h> /*内核定时器*/

#include <asm-generic/poll.h>

#include <linux/poll.h> /* poll机制*/

#include <linux/platform_device.h> /* 平台设备驱动相关头文件*/

#include <linux/rtc.h>

#include <linux/gpio.h>

#include <mach/gpio.h>

#include <plat/gpio-cfg.h>

#include <linux/delay.h>

/*--------------------------------DS1302相关操作代码---------------------------------------------*/

static unsigned char RTC_bin2bcd(unsigned val)

{

return ((val/10)<<4)+val%10;

}

static unsigned RTC_bcd2bin(unsigned char val)

{

return (val&0x0f)+(val>>4)*10;

}

/*

函数功能:DS1302初始化

Tiny4412硬件连接:

CLK :GPB_4

DAT :GPB_5

RST :GPB_6

*/

void DS1302IO_Init(void)

{

/*1. 注册GPIO*/

gpio_request(EXYNOS4_GPB(4), "DS1302_CLK");

gpio_request(EXYNOS4_GPB(5), "DS1302_DAT");

gpio_request(EXYNOS4_GPB(6), "DS1302_RST");

/*2. 配置GPIO口模式*/

s3c_gpio_cfgpin(EXYNOS4_GPB(4), S3C_GPIO_OUTPUT); //时钟

s3c_gpio_cfgpin(EXYNOS4_GPB(5), S3C_GPIO_OUTPUT); //数据

// s3c_gpio_cfgpin(EXYNOS4_GPB(2), S3C_GPIO_INPUT); //输入模式

s3c_gpio_cfgpin(EXYNOS4_GPB(6), S3C_GPIO_OUTPUT); //复位

/*3. 上拉GPIO口*/

gpio_set_value(EXYNOS4_GPB(4), 1); //CLK

gpio_set_value(EXYNOS4_GPB(5), 1); //DAT

gpio_set_value(EXYNOS4_GPB(6), 1); //RST

gpio_set_value(EXYNOS4_GPB(6), 0); //RST脚置低

gpio_set_value(EXYNOS4_GPB(4), 0); //SCK脚置低

}

//#define RTC_CMD_READ 0x81 /* Read command */

//#define RTC_CMD_WRITE 0x80 /* Write command */

//#define RTC_ADDR_RAM0 0x20 /* Address of RAM0 */

//#define RTC_ADDR_TCR 0x08 /* Address of trickle charge register */

//#define RTC_ADDR_YEAR 0x06 /* Address of year register */

//#define RTC_ADDR_DAY 0x05 /* Address of day of week register */

//#define RTC_ADDR_MON 0x04 /* Address of month register */

//#define RTC_ADDR_DATE 0x03 /* Address of day of month register */

//#define RTC_ADDR_HOUR 0x02 /* Address of hour register */

//#define RTC_ADDR_MIN 0x01 /* Address of minute register */

//#define RTC_ADDR_SEC 0x00 /* Address of second register */

//DS1302地址定义

#define ds1302_sec_add 0x80 //秒数据地址

#define ds1302_min_add 0x82 //分数据地址

#define ds1302_hr_add 0x84 //时数据地址

#define ds1302_date_add 0x86 //日数据地址

#define ds1302_month_add 0x88 //月数据地址

#define ds1302_day_add 0x8a //星期数据地址

#define ds1302_year_add 0x8c //年数据地址

#define ds1302_control_add 0x8e //控制数据地址

#define ds1302_charger_add 0x90

#define ds1302_clkburst_add 0xbe

//初始时间定义

static unsigned char time_buf[8] = {0x20,0x10,0x06,0x01,0x23,0x59,0x55,0x02};//初始时间2010年6月1号23点59分55秒 星期二

static unsigned char readtime[14];//当前时间

static unsigned char sec_buf=0; //秒缓存

static unsigned char sec_flag=0; //秒标志位

//向DS1302写入一字节数据

static void ds1302_write_byte(unsigned char addr, unsigned char d)

{

unsigned char i;

gpio_set_value(EXYNOS4_GPB(6), 1); //启动DS1302总线

//写入目标地址:addr

addr = addr & 0xFE; //最低位置零,寄存器0位为0时写,为1时读

for(i=0;i<8;i++)

{

if(addr&0x01){gpio_set_value(EXYNOS4_GPB(5), 1);}

else{gpio_set_value(EXYNOS4_GPB(5), 0);}

gpio_set_value(EXYNOS4_GPB(4), 1); //产生时钟

gpio_set_value(EXYNOS4_GPB(4), 0);

addr=addr >> 1;

}

//写入数据:d

for(i=0;i<8;i++)

{

if(d & 0x01) {gpio_set_value(EXYNOS4_GPB(5), 1);}

else {gpio_set_value(EXYNOS4_GPB(5), 0);}

gpio_set_value(EXYNOS4_GPB(4), 1); //产生时钟

gpio_set_value(EXYNOS4_GPB(4), 0);

d = d >> 1;

}

gpio_set_value(EXYNOS4_GPB(6), 0); //停止DS1302总线

}

//从DS1302读出一字节数据

static unsigned char ds1302_read_byte(unsigned char addr)

{

unsigned char i,temp;

gpio_set_value(EXYNOS4_GPB(6), 1);//启动DS1302总线

//写入目标地址:addr

addr=addr | 0x01; //最低位置高,寄存器0位为0时写,为1时读

for(i=0; i<8; i++)

{

if(addr & 0x01){gpio_set_value(EXYNOS4_GPB(5), 1);}

else {gpio_set_value(EXYNOS4_GPB(5), 0);}

gpio_set_value(EXYNOS4_GPB(4), 1);

gpio_set_value(EXYNOS4_GPB(4), 0);

addr=addr >> 1;

}

s3c_gpio_cfgpin(EXYNOS4_GPB(5), S3C_GPIO_INPUT); //输入模式

//输出数据:temp

for(i=0; i<8; i++)

{

temp=temp>>1;

if(gpio_get_value(EXYNOS4_GPB(5))){temp |= 0x80;}

else{temp&=0x7F;}

gpio_set_value(EXYNOS4_GPB(4), 1);

gpio_set_value(EXYNOS4_GPB(4), 0);

}

s3c_gpio_cfgpin(EXYNOS4_GPB(5), S3C_GPIO_OUTPUT); //输出模式

gpio_set_value(EXYNOS4_GPB(6), 0); //停止DS1302总线

return temp;

}

//向DS302写入时钟数据

static void ds1302_write_time(struct rtc_time *time)

{

ds1302_write_byte(ds1302_control_add,0x00); //关闭写保护

ds1302_write_byte(ds1302_sec_add,0x80); //暂停时钟

//ds1302_write_byte(ds1302_charger_add,0xa9); //涓流充电

/*设置RTC时间*/

//因为DS1302的年份只能设置后两位,所有需要使用正常的年份减去2000,得到实际的后两位

ds1302_write_byte(ds1302_year_add,RTC_bin2bcd(time->tm_year-2000)); //年

ds1302_write_byte(ds1302_month_add,RTC_bin2bcd(time->tm_mon)); //月

ds1302_write_byte(ds1302_date_add,RTC_bin2bcd(time->tm_mday)); //日

ds1302_write_byte(ds1302_hr_add,RTC_bin2bcd(time->tm_hour)); //时

ds1302_write_byte(ds1302_min_add,RTC_bin2bcd(time->tm_min)); //分

ds1302_write_byte(ds1302_sec_add,RTC_bin2bcd(time->tm_sec)); //秒

//ds1302_write_byte(ds1302_day_add,RTC_bin2bcd(time->tm_wday)); //周 time->tm_wday一周中的某一天

ds1302_write_byte(ds1302_control_add,0x80); //打开写保护

}

static int DS1302_rtc_ioctl(struct device *dev, unsigned int cmd,unsigned long arg)

{

/*设置RTC时间*/

struct rtc_time time;

copy_from_user(&time,(const void __user *)arg,sizeof(struct rtc_time));

ds1302_write_time(&time);

return 0;

}

//此函数通过应用层的ioctl的RTC_RD_TIME命令进行调用

static int tiny4412_rtc_gettime(struct device *dev, struct rtc_time *rtc_tm)

{

rtc_tm->tm_year=RTC_bcd2bin(ds1302_read_byte(ds1302_year_add))+2000; //年

rtc_tm->tm_mon=RTC_bcd2bin(ds1302_read_byte(ds1302_month_add)); //月

rtc_tm->tm_mday=RTC_bcd2bin(ds1302_read_byte(ds1302_date_add)); //日

rtc_tm->tm_hour=RTC_bcd2bin(ds1302_read_byte(ds1302_hr_add)); //时

rtc_tm->tm_min=RTC_bcd2bin(ds1302_read_byte(ds1302_min_add)); //分

rtc_tm->tm_sec=RTC_bcd2bin((ds1302_read_byte(ds1302_sec_add))&0x7f);//秒,屏蔽秒的第7位,避免超出59

//time_buf[7]=ds1302_read_byte(ds1302_day_add); //周

return 0;

}

//此函数通过应用层的ioctl的RTC_SET_TIME命令进行调用

static int tiny4412_rtc_settime(struct device *dev, struct rtc_time *tm)

{

ds1302_write_time(tm);

return 0;

}

/*RTC文件操作*/

static const struct rtc_class_ops DS1302_rtcops = {

.ioctl=DS1302_rtc_ioctl,

.read_time = tiny4412_rtc_gettime,

.set_time = tiny4412_rtc_settime

};

static struct rtc_device *rtc=NULL;

/*当设备匹配成功执行的函数-资源探查函数*/

static int drv_probe(struct platform_device *pdev)

{

rtc = rtc_device_register("DS1302RTC",&pdev->dev, &DS1302_rtcops,THIS_MODULE);

if(rtc==NULL)

printk("RTC驱动注册失败1\n");

else

{

printk("RTC驱动注册成功1\n");

}

/*1. 初始化GPIO口*/

DS1302IO_Init();

msleep(10);

return 0;

}

static int drv_remove(struct platform_device *dev)/*当设备卸载后调用这条函数*/

{

/*释放GPIO口*/

gpio_free(EXYNOS4_GPB(4));

gpio_free(EXYNOS4_GPB(5));

gpio_free(EXYNOS4_GPB(6));

rtc_device_unregister(rtc);

printk("RTC驱动卸载成功\n");

return 0;

}

/*平台设备驱动端结构体-包含和probe匹配的设备名字*/

struct platform_driver drv=

{

.probe = drv_probe, /*需要创建一个probe函数,这个函数是对设备进行操作*/

.remove = drv_remove, /*创建一个remove函数,用于设备退出*/

.driver =

{

.name = "DS1302rtc", /*设备名称,用来与设备端匹配(非常重要)*/

},

};

/*平台驱动端的入口函数*/

static int __init plat_drv_init(void)

{

platform_driver_register(&drv);/*注册平台驱动*/

return 0;

}

/*平台驱动端的出口函数*/

static void __exit plat_drv_exit(void)

{

platform_driver_unregister(&drv);/*释放平台驱动*/

}

module_init(plat_drv_init); /*驱动模块的入口*/

module_exit(plat_drv_exit); /*驱动模块的出口*/

MODULE_LICENSE("GPL"); /*驱动的许可证-声明*/DS1320设备端代码

#include "linux/module.h"

#include "linux/init.h"

#include <linux/platform_device.h>

/*

* device 设备端

*/

//释放平台总线

static void pdev_release(struct device *dev)

{

printk("rtc_pdev:the rtc_pdev is close!!!\n");

}

/*设备端结构体*/

struct platform_device rtc_pdev= /*设备结构体,设备名字很重要!*/

{

.name = "DS1302rtc", /*设备名*/

.id = -1, /*-1表示创建成功后这边设备的名字就叫myled,若该值为0,1则设备名是myled.0,myled.1...*/

.dev = /*驱动卸载时调用*/

{

.release = pdev_release,/*释放资源*/

},

};

/*平台设备端入口函数*/

static int __init plat_dev_init(void)

{

platform_device_register(&rtc_pdev);/*注册平台设备端*/

return 0;

}

/*平台设备端出口函数*/

static void __exit plat_dev_exit(void)

{

platform_device_unregister(&rtc_pdev);/*注销平台设备端*/

}

module_init(plat_dev_init);

module_exit(plat_dev_exit);

MODULE_LICENSE("GPL");

/* DDR model number: MT40A1G16KNR-062E:E */

#ifdef CONFIG_SYS_DDR_RAW_TIMING

dimm_params_t ddr_raw_timing = {

.n_ranks = 1, /* Number of ranks/ chip selects of DDR */

.rank_density = 8589934592u, /* this is size in one rank, here 8GB */

.capacity = 8589934592u, /* this is the total size, here 8GB */

.primary_sdram_width = 64, /* this is the data bus width */

.ec_sdram_width = 8, /* this is the ECC data width */

.die_density = 0x5, /* this is each DRAM die density, here twin 8Gbit die density. 0x44Gbit, 0x58Gbit, 0x616Gbit*/

.registered_dimm = 0, /* if register chip is used similar to an RDIMM = 1, otherwise = 0 */

.mirrored_dimm = 0, /* =1 if C/A bus mirroring is used, all UDIMMs with two ranks are mirrored */

.n_row_addr = 16, /* number of rows from dram datasheet */

.n_col_addr = 10, /* number of columns from dram datasheet */

.bank_addr_bits = 0, /* for DDR4 this is always = 0 defining two bits bank address in DRAM */

.bank_group_bits = 2, /* for x16 dram = 1, 1-bit BG, for x8 dram = 2, 2-bits for BG */

.edc_config = 2, /* leave as is, does not change. 0no ECC, 2 ECC*/

.burst_lengths_bitmask = 0x0c, /* leave as is, this is needed for uboot masking, does not change */

.tckmin_x_ps = 625, /* tck min = 625ps from DRAM datasheet */

.tckmax_ps = 1500, /* tck max = 1500ps from DRAM datasheet */

.caslat_x = 0x00FFFA00, /* leave as is, this is needed for uboot masking, does not change */

.taa_ps = 13750, /* tAA from DRAM datasheet (ps)*/

.trcd_ps = 13750, /* tRCD from DRAM datasheet (ps) */

.trp_ps = 13750, /* tRP from DRAM datasheet (ps)*/

.tras_ps = 32000, /* tRAS from DRAM datasheet (ps) */

.trc_ps = 45750, /* tRC = tRP+tRCD or from DRAM datasheet (ps)*/

.trfc1_ps = 350000, /* tRFC1 from DRAM datasheet (ps)*/

.trfc2_ps = 260000, /* tRFC2 from DRAM datasheet (ps)*/

.trfc4_ps = 160000, /* tRFC4 from DRAM datasheet (ps)*/

.tfaw_ps = 21000, /* tFAW from DRAM datasheet (ps)*/

.trrds_ps = 2500, /* tRRD_S from DRAM datasheet (ps)*/

.trrdl_ps = 4900, /* tRRD_L from DRAM datasheet (ps)*/

.tccdl_ps = 5000, /* tCCD_L from DRAM datasheet (ps)*/

.refresh_rate_ps = 7800000, /* tREFI from DRAM datasheet (ps)*/

};